缓冲寄存器的结构和工作原理 -

来源: 网络用户发布,如有版权联系网管删除 2018-09-06

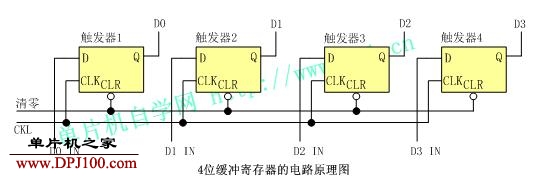

[导读]它是用来暂存某个数据,以便在适当的时间节拍和给定的计算步骤将数据输入或输出到其它记忆单元中去,下图是一个并行输入、并行输出的4位缓冲器的电路原理图,它由4个D触发器组成。启动时,先在清零端加清零脉冲,把各

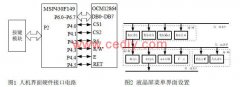

它是用来暂存某个数据,以便在适当的时间节拍和给定的计算步骤将数据输入或输出到其它记忆单元中去,下图是一个并行输入、并行输出的4位缓冲器的电路原理图,它由4个D触发器组成。

本文引用地址: http://www.21ic.com/app/mcu/201807/779902.htm

启动时,先在清零端加清零脉冲,把各触发器置0,即Q端为0。然后,把数据加到触发器的D输入端,在CLK时钟信号作用下,输入端的信息就保存在各触发器中(D0~D3)。

图片1

查看评论 回复