S3C2440FCLK、HCLK、PCLK的配置 -

[导读] /****************************************************** *说 明: S3C2440FCLK、HCLK、PCLK的配置 ******************************************************/ 三星官方搭载的wince系统的FLCK值为400MHz,HCLK值为

/******************************************************

*说 明: S3C2440FCLK、HCLK、PCLK的配置

本文引用地址: http://www.21ic.com/app/mcu/201807/783527.htm

******************************************************/

三星官方搭载的wince系统的FLCK值为400MHz,HCLK值为100MHz、PCLK值为50MHz。那么这些值通过什么方法计算出来呢?大概过程如下,这些值在外部晶振12MHz的基础上通过PLL的作用倍频到我们需要的核心频率如400MHz,由于该频率过高,需要通过对预分频器进行适当的设置获取外围设备能够正常工作的频率如HCLK 100MHz、PLCK 50MHz。

在这里有必要说明FCLK、HCLK、PCLK的含义,FCLK为内核时钟,HCLK为总线时钟(包括USB时钟),PCLK为I/O接口时钟(如常用的SPI、I2C、UART的时钟配置都是通过PCLK时钟为基准的)。

在WINCE6.0 BSP中,设置MPLLCON与设置CLKDINV的代码如下:

;设置MPLLCON

ldr r0, = MPLLCON

ldr r1, = ((92 << 12) + (1 << 4) + 1)

str r1, [r0]

MPLLCON的配置是用来确定FCLK频率的,计算公式如下:

图1 计算FLCK

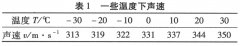

从“ldr r1, = ((92 << 12) + (1 << 4) + 1) ”该代码中可以看到数值存在移位操作,即92<<12、1<<4,这个可以参考图2各预分频值的配置。

图2 MDIV、PDIV、SDIV

MDIV的配置在MPLLCON的[19:12]位,因此配置MDIV的值需要左移12位。同样的道理,配置PDIV值需要左移4位,SDIV值需要左移0位(左移0位相当于不用偏移,废话,嘻嘻)。

那么根据图1计算FLCK的公式,计算过程如下:

FCLK=2*(92+8)*(12000000)/(3+2^1)=400000000=400MHz

当FCLK得到正确的配置后,这时就需要对HCLK、FCLK进行配置了,即进行预分频操作,该配置过程很见到,只需要对CLKDIVN简单配置一下就OK了。

CLKDIVN寄存器内容如图3。

;设置CLKDIVN

ldr r0,=CLKDIVN

ldr r1,=0x5

str r1,[r0]

在bsp中CLKDIVN的配置值为0x5,即FCLK:HCLK:PCLK=1:4:8。相对应的频率将会是400MHz、100MHz、50MHz。

查看评论 回复