UART0串口编程系列(二) -

[导读]

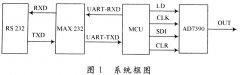

三.中断方式的串口编程1.用中断方式编写串口程序由那几部分组成2.硬件上的支持1>UART0发送FIFO缓冲区A.UART0含有1个16字节的发送FIFO缓冲区B.U0THR是UART0发送FIFO的最高字节C.UART的发送FIFO是一直

三.中断方式的串口编程

本文引用地址: http://www.21ic.com/app/mcu/201808/765775.htm

1.用中断方式编写串口程序由那几部分组成

2.硬件上的支持

1>UART0发送FIFO缓冲区

A.UART0含有1个16字节的发送FIFO缓冲区

B.U0THR是UART0发送FIFO的最高字节

C.UART的发送FIFO是一直使能的

2>UART0接收FIFO缓冲区

A.UART0含有一个16字节的接收FIFO缓冲区。

B.软件设置接收FIFO缓冲区的触发字节。

3>中断接口:UART0的中断接口包含中断使能寄存器(U0IER)和中断标识寄存器(U0IIR)。

lU0IIR:提供状态码用于指示一个挂起中断的中断源和优先级。

lU0IER可以控制UART0的4个中断源。

4>UART0有4个中断源:

A.RLS(接收线状态)中断:

(1)优先级最高

(2)它在以下条件发生时产生错误

l帧错误(FE)

l溢出错误(OE)

l奇偶错误(PE)

l间隔中断(BI)

注:

?可以通过查看U0LSR[4:1]中的值看到产生该中断的错误条件

?读取U0LSR寄存器时清除该中断。

B.RDA(接收数据可用)中断:

(1)与CTI中断并列第二优先级。

(2)在以下情况触发中断:

l当接收的有效数据到达接收FIFO设置寄存器(U0FCR)中设置的触发点时,RDA被激活。当接收FIFO中的有效数据少于触发点时,RDA复位。

l中断过程:

1>移位寄存器(U0RSR)从RxD引脚接收串行数据后,送入接收FIFO中

2>当接收FIFO中的有效数据数量达到预定的触发点时,置位RDA中断。

3>从U0RBR寄存器中读取FIFO中最早到达的数据,当FIFO中的有效数据小于触发点时,清零RDA中断。

C.CTI(字符超时指示)中断

(1)优先级为2.

(2)在以下情况发生中断:

l当接收FIFO中的有效数据少于预定的触发点数量时,如果在一定时间内仍没有接收到新的数据,那将触发该中断。

(3)上面的时间指的是:3.5~4.5个字节所需要的时间。

(4)对接收FIFO的任何操作都会清零该中断标志。

(5)中断过程:

l移位寄存器(U0RSR)从RxD0引脚接收串行数据后,送入接收FIFO中。

l当接收FIFO中的有效数据少于触发个数,但如果长时间没有数据到达,则触发CTI中断。

l从U0RBR中读取接收FIFO中的数据,或者有新的数据送入接收FIFO,都将清零CTI中断。

注:

?3.5~4.5个字节的时间:指在串口当前的波特率下,发送3.5~4.5个字节所需要的时间。

?当接收FIFO中存放多个数据,从U0RBR读取数据,但是没有读完所有数据,那么在经过3.5~4.5个字节的时间后触发CTI中断。

D.THRE(发送)中断

(1)优先级为第三级优先级。

(2)当FIFO为空并且在以下情况触发中断:

l系统启动时,虽然发送FIFO为空,但不会产生THRE中断。

l在上一次发生THRE中断后,向发送FIFO中写入1个字节数据,将在一个字节加上一个停止位后发生THRE中断

(because:如果发送移位寄存器为空,那么写入发送FIFO的数据将直接进入发送移位寄存器。此时发送FIFO仍然为空,如果立即产生THRE中断,就会影响紧接着写入发送FIFO的数据。

所以在发送完该一个字节以及一个停止位后,才产生THRE中断。

l如果在发送FIFO中有过两个字节以上的数据,但是现在发送FIFO为空时,将立即触发THRE中断。

l当THRE中断为当前有效的最高优先级中断时,往U0THR写数或者对U0IIR的读操作,将使THRE中断复位

我们来看看这些中断源与存储器之间的关系:

注:

?由上图可知:UART0有4个中断源:分别是RLS(线状态)中断,RDA(接收数据)中断,CTI(字符超时)中断,THRE(发送数据)中断。

?4个中断源的优先级如下图所示:

3.串口中断接收初始化

1>串口中断接收初始化流程

l设置I/O引脚连接到UART0

l置位除数锁存位,配置UART0帧数据格式

l根据波特率计算分频值

l设置波特率

l清除除数锁存位,并设置工作模式

l使能FIFO,并设置触发点

l允许RBR中断

注:我们可以发现与轮训方式相比,中断方式只是增加了使能FIFO,并设置中断触发点和允许RBR中断两步。

2>中断串口初始化需要配置的寄存器

(与轮循方式配置方法相同的寄存器在此处不在涉及)

lU0FCR(FIFO控制寄存器):U0FCR控制UART0 Rx和Tx FIFO的操作。

lU0IER(中断使能寄存器):U0IER用于使能4个UART0中断源。

3>具体寄存器的配置

(1)U0FCR

A作用:控制UART0 Rx和Tx的操作。

B长度:8位寄存器。

C:每一位的含义:

l第0位:表示FIFO使能

置1:表示使能对UART0 Rx和Tx的FIFO以及U0FCR[7:1]的访问。

置0:表示不能使用Rx和Tx的FIFO以及步能对U0FCR[7:1]的访问。

注:该位的任何变化都将使UART0 FIFO清空。

l第1位:表示Rx FIFO的复位。

置1:会清零UART0 RxFIFO中的所有字节并复位指针逻辑。该位自动清零。

l第2位:表示Tx FIFO的复位。

置1:会清零UART0 TxFIFO中的所有字节并复位指针逻辑。改位自动清零。

l第[5:3]位:保留位,用户不能对其进行操作。从保留位读出的值未被定义。

l第[7:6]位:表示Rx触发选择

00:触发点为0(默认为1字节)

01:触发点为1(默认为4字节)

10:触发点为2(默认为8字节)

11:触发点为3(默认为14字节)

注:这两个位决定在激活中断之前,接收UART0 FIFO必须写入个字符。

(2)U0IER(中断使能寄存器)

A作用:U0IER用于使能4个UART0中断源

B长度:8位寄存器

C每一位的含义:

l第0位:表示RBR中断使能

置1:使能RDA中断

置0:禁止RDA中断

注:U0IEER第零位使能UART0接收数据可用中断。它还控制(CTI)字符接收超时中断。

l第1位:表示THRE中断使能

置1:使能THRE中断

置0:禁止THRE中断

l第2位:表示Rx线状态中断使能

置1:使能Rx线状态中断

置0:禁止RX线状态中断

注:U0IER第二位使能UART0 Rx线状态中断。该中断的状态可从U0LSR[4:1]读出

l第[7:3]位:是保留位

注:用户不能向其写入1.

4>串口初始化程序:

***********************************************************

*作者:tiger-john

*时间:2011年1月18日

*名称:UART0_Init

*功能:UART0初始化通讯波特率115200,8位数据位,1位停止位,无奇偶校验

*接收FIFO触发点为8字节,使能RDR(接收数据)中断

*入口参数:bps串口波特率

*出口参数:无

****************************************************************************/

voidUART0_Init(uint32 bps)

{

uint16Fdiv;

PINSEL0 = (PINSEL0 & ~(0xf) " 0x05) ;//设置UART0的引脚

U0LCR = 0x83;//置为除数锁存位,进行配置

Fdiv = (Fpclk>>4)/bps;

U0DLM = Fdiv>>8;

U0DLL = Fdiv%256;

U0LCR = 0x03;//清除除数锁存位,并设置工作模式

U0FCR = 0x81;//使能FIFO,并设置触发点为8字节

U0IER = 0x01;//允许RBR中断,即接收中断

}

5.中断初始化

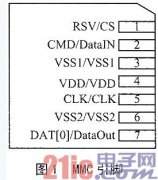

先来看一下UART0和VIC之间的关系:

1>中断初始化流程:

l选择中断为向量中断或快速中断

l分配中断通道

l设置UART0向量地址

l使能UART0中断

2>关于ARM中断编程方法和寄存器的使用在此不做涉及(如果想知道的话,可以看这篇文章http://blog.csdn.net/tigerjb/archive/2010/11/30/6045409.aspx

3>中断初始化程序:

/**********************************************************

*作者:tiger-john

*时间:2011年1月18日

* 名称: Interrupt_Init

查看评论 回复