����Ƶ�������ֲ��28nm���ƶ���ý��оƬϵͳ - ��ģ��� -

����

������Ƶ���������ֻ���ƽ����Ե����ѵ���Ӧ�ú��������������IJ�Ʒ�dz���Ҫ��������������ǹؼ���Ʊ������г�Ҫ���и������߱��棨Hi-Fi����ƵЧ��������������֤���Ż�����ƵIP����ʵ���ض�����Ƶ���ܣ��������͵�����ý��оƬϵͳ�Ĺ��ġ�����ͳɱ���

��������������ɵ�28�����ռ�����������Ƶ������һ��ս������Ӹ��ӣ�ԭ����ģ���·������ѭĦ�����ɣ�Ҳ�������Ź��շ�չ���ߴ��С������28�����յľ�Բ�ɱ����65����40�����ռ����߳����ࡣ���ֵ�·��ѭĦ�����ɣ���Ȼ��Բ�ɱ���ߣ������������ܺ��ܶ�Ҳ�����ˡ���Ƶ����������õ�ģ���·һ��ʹ��IO��������˲��������ֵ�·����ʹ���ں�������core device������С�ߴ硣������Բ�ɱ����ӵ�ͬʱ��ģ���·�������ܲ�û�и��ƣ����Ҳû�м�С����˱��뿪���µļܹ��Լ�������������磬����65�����������Ϊ2.5ƽ��������Ƶ����������ڲ���28�������������Ҫ��С��1.9ƽ�����ײ���ʹ��ɱ�������ͬ��������25%����ļ�С�����˶Ը����սڵ���Ƶ��������Ĺؼ���ս��

���������о��˽���Ƶ���ܼ�����28�����ƶ���ý��оƬϵͳ�������ٵ���Ҫϵͳ��������ս���Լ����ͨ�����¼���Ӧ����Щ��ս��

����������Ħ�����ɣ������ֹ��ܴ�ģ�����������ʵ�֣�

�����������ƣ�֧��оƬϵͳͨ�òο�ʱ�ӵ���Ƶ�������ʣ�

���������úõ�Դ��ѹ���ͺ�����֮���ƽ�⣻

������ �����˽�оƬϵͳ֮���ϵͳ���ܻ��֣�

������ʶ���д�ʩ��ʹϵͳ�ɱ���С���������Ա��ϵͳ�ܹ�ʦ���ܹ����ֳɱ������ܺ�����֮�����Чƽ�⣬ʹ�����ܹ�Ƕ����ƵIP����������������Ӷ��������ǵ�SOC�ھ�����ʤ����

������Ƶ�����������֪ʶ

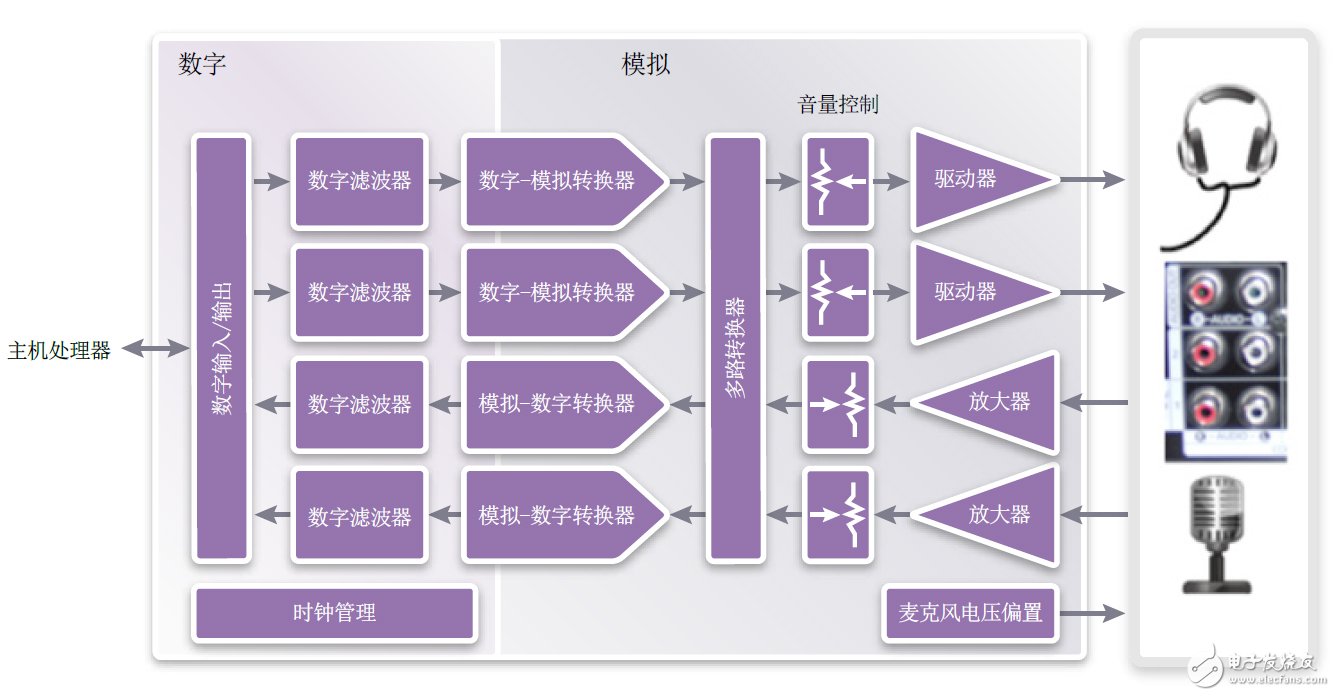

������Ƶ���������Ҫ����������ת����ģ����ɣ�������¼����ģ��-����ת������ADC�������ڻطŵ�����-ģ�����DAC�������������������������������Щģ��ᱻ�ֱ��ơ�ͼ1�ǵ��͵���������Ƶ���������ͼ�� ͼ����¼���������������������ƵķŴ������ɽ�С�ź���˷�ʹ��ź����µ�����ģ��-����ת���������뷶Χ���ط����������ܹ�ֱ������������С���������Ŵ�ÿ·���ֱ�����������ƹ��ܡ�������ṩ��˷�ƫ�õĵ�������Դ��

�������ֵ�·�ж�����ֹ��ɣ�����Ҫ����������Ƶ�˲��������ɽ���������ת��Ϊ����ת�����Ĺ�����ʱ�ӣ���������Ƶ����ĸ�Ƶ������ʱ�ӹ���Ҳ����Ҫ������ȷ����ͬ���ʵ�ģ��˴˱���ͬ������֧�ֶ��ֲ������ʡ�

����ͼ1����Ƶ������������Կ�ͼ

������Ƶ�����������֪ʶ

����������Ч��28������Ƶ��������ĵ�һ�������ø��Ƚ��Ĺ��ռ������������������ܡ�����28�����������������������ƣ���ˣ����ǵ���Ƶ����ʦ����ܶ����Ƿ�������ڵ�Ǩ�ơ��������ϵͳ�ܹ���������ʵ�־����ܶ�Ĺ��ܡ�ͨ����������źŴ�����ģ����ת�����������������ڡ���Ϻ��л�����Ƶ����������������Ƚ����ա�����ǣ�����ת�����Ƶ������ӿڸ����ĵط����Ӷ�����ģ�Ⲽ�֣����������������������������������Ƚ����ա�

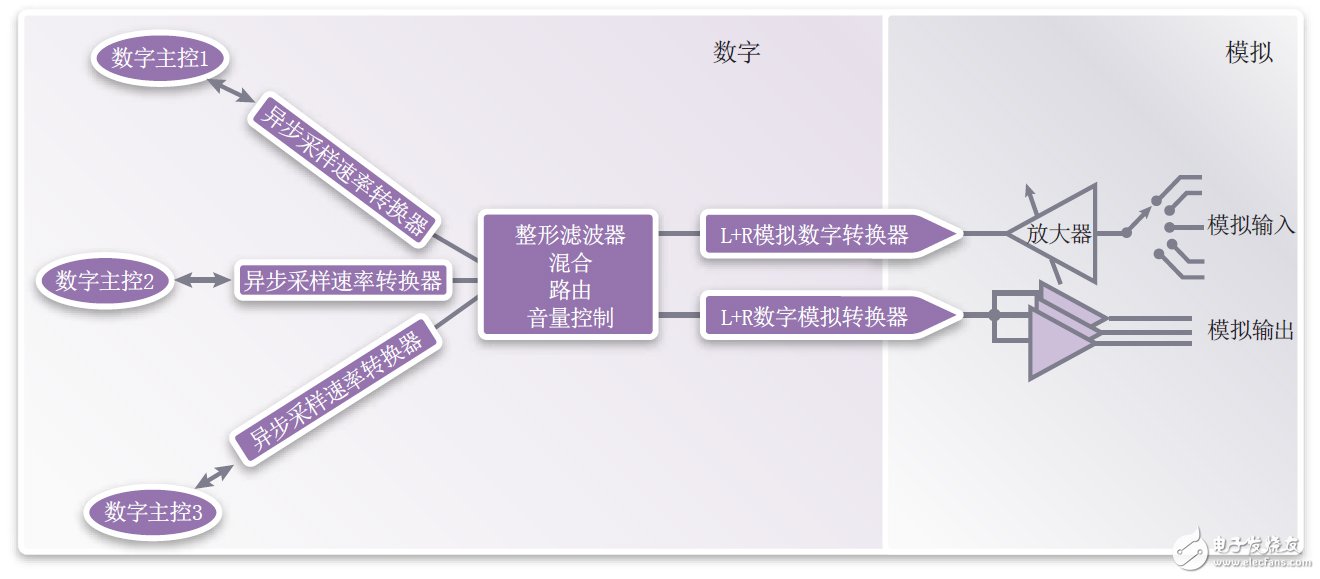

����ͨ���������źŴ�����ģ����Ǩ�Ƶ���������Ƶ�����������߷���Ħ�����ɵ����ֵ�·������������ģ���·�������������������Ϊ���ĵ��¼ܹ����������¼ܹ��У������źŴ�����������ģ��ִ�У��ܱ�ģ���·��������ת�������첽��������ת������ASRC������ͼ2��ASRC����������һ������ϸ���ܡ�

�����ִ��ƶ���ý��ϵͳ�п����ж���������أ�ȫ���ڸ��Ե�ʱ�������С����磬���������������������ʽ���ߵ��ͨѶ��Ӧ�ô���������������ϵͳ�����ý���ļ������������ɵ�·��IC���������������������ܱ��豸��ÿ���������ض��ֱ����첽ʱ���������С���ˣ���һϵͳ�е���Ƶ��������������������ģ����֮����������������һ���������̬ϵͳ�в�ͬʱ����֮����л���ͨѶ��

����ͼ2������������Ƶ���ؽ���������Ϊ���ĵ���Ƶ����

����������֧�ֶ��ʱ������

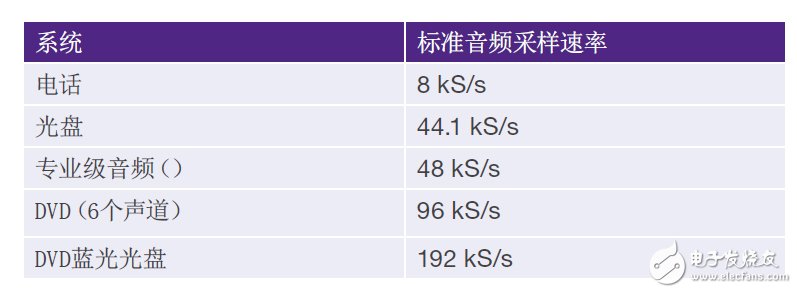

���������������غ�ʱ�������Ƶ����������ر��ǶԸ߶ȼ��ɵ�28����оƬϵͳ�������һ����ս������ͬ�����ʶ�������Ƶ���������1��ʾ����Ƶ�������������ת����Ҫ���ʱ��ȡ������Ƶ���ݲ������ʺ�����Ӧ����оƬϵͳ�ϵ�ʱ�ӡ����ڴ��ڶ�����Ƶ�������ʺ�������ʱ�ӣ����ǵ�����൱���ӡ������˲�����Ϊ�����һ���ⷢ����Ҫ���ã�ԭ�������ǿ��Դ���������Ƶ�ӿں���Ƶ����ת����֮������ݲ���������ܹ����в�������ת����

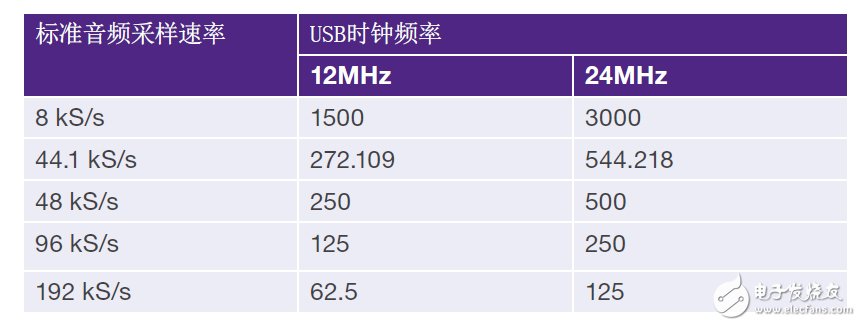

������1������Ƶ��������

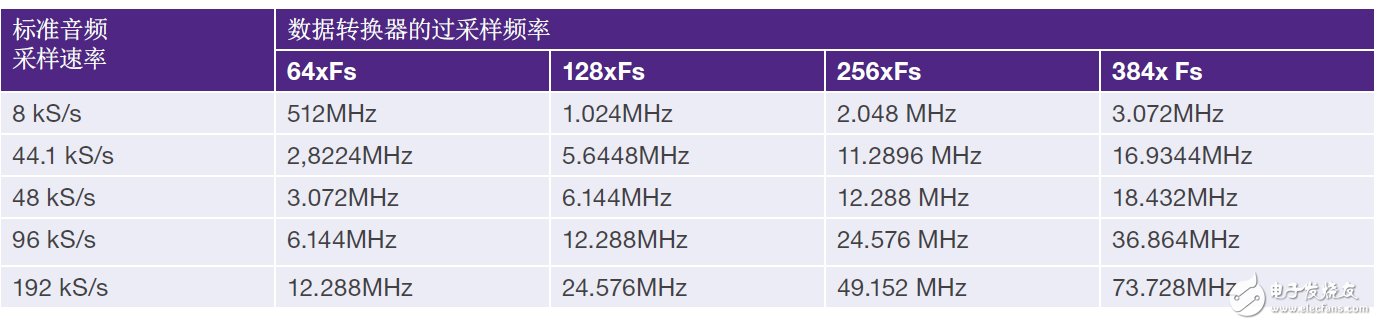

������������ת���������Թ�����Ƶ�ʣ�ͨ����128X��256X�����У���������ת�����������ʱ��Ƶ�ʽ���5-12MHz��Χ����ˣ���Ƶ�����������֧�ָ��ֲ�ͬ����Ƶ�������ʣ�����Ӧ��ʱ��Ƶ�ʣ���������Ӧ���м��ɡ����ǣ����ڴ��ڶ���ʱ��Ƶ�ʱ��ʵ��������Լ�����Ŀ��ʵ����������ֱ�ӡ���ˣ������˲������������������ת�����á���2����Ƶ�������ʺͲ�������ת����ͬ��ϵij��ò���Ƶ�ʡ�

������2����Ƶ�������ʺͲ�������ת����ͬ��ϵij��ò���Ƶ��

����Ϊ����Ӧ�����������ʺͿ���ʱ�ӵ���ϣ������Ա�ɲ��ø��ּ��ɣ������һ���֡�

��������1����Ƶʱ��ʹ�����·

��������һЩ������ռ��/��ɱ������ƣ�����Ӧ����ʹ����Ƶ�������ר�õľ�����������Ƶ������������ܹ�֧������������ʱ�ӵIJ�ͬ��Ƶ���ʣ�ͨ����USBʱ�ӵ�12MHz�����ı����������·��PLL����������������Ҫ����Ƶʱ�ӡ�����Ҫ��dz��õ�Ƶ�ʷֱ�����֧������Ƶ������ң�ͬʱҪ�ṩ�Ͷ������ʱ�ӣ�������·������Ҫ����һ��������ҡ���ˣ���ò��ò�Ҫ�����·���������������

��������2���ظ�ʹ��û�����·��USBʱ��

����һ�������������Dz���û�����·�ļ��������ظ�ʹ��USBʱ�Ӻͱ���Ϊ��Ƶ����ר�����·��USB�Ƿdz����ܻ�ӭ�Ľӿڣ��������ձ����������Ӧ���С�12MHz��24MHz��ʱ�Ӷ���ʹ�ã����ǵĶ�����Խϵͣ���������Ƶ����ҪҪ��24MHz USBʱ�ӿ�֧��48kS/s��Ƶ���ʼ��䱶������Ƶ���ʣ���96kS/s��192kS/s����Ϊ��������������24��000=125x192����Ҫʹ��24MHz USBʱ�ӣ���Ҫ���˲�����������ת���ӱ�Ƶ�128����������Ϊ125����

�������ǣ�44.1kS/s��Ƶ����ֻ�ܽ������ɡ�����136����������ת������Ƶʱ�ӿɴ�Լ�ﵽ44.1176kS/s������ֵ���в�ͬ���������ֲ��dz�С�����Ըо�����ʵ�������߽���0.04%�ı仯������С�ı仯�Ȱ�����Сһ�ٱ�������0.04%�Ļط��ٶȻᵼ��3���ӵĸ�����ǰ10���������

������3�г���12MHz��24MHz USBʱ�ӻ�����ͨ����Ƶ�������ʵ�ת���������������������44.1kHz��Ƶ��������ת����������������

������3��USBʱ��Ƶ������Ƶʱ�Ӳ�������

��������3�����ò�������ת����

������Ƶ����ʱ����������ת������SRC����������Ժͼ����ԣ���˳����벻�����·�ļ��������һ��ʹ�á�������˵�������˲����ı������ݲ���Ƶ�ʡ��������������Ƶ�ʣ��ϲ��������С����Ƶ�ʣ��²������������ԡ�ͬ�����͡��첽�����С������ͬ����������ת����������������ʹ̶���������첽��������ת����������������ʵ�����֮һ����߶������仯���˲������Զ��������á����������ʹ��㷨�������������������������֮��ı��ʡ���ϵͳ�Ľ��������롰���������ɵ����ľ���������ʱ����ƵԴ��ʱ���첽��������ת������ASRCs��ͨ�����õ���

��������Ӧ����Ҫ�Բ�ͬ�IJ�����������ƵԴ֮���·ѡ��ͨ��ASRC�ز���������ʱ�ӣ���������Ϊ44.1kS/s�����ݿ�����48kS/s����������һ����ж�·ѡ��

����ͬ���Ĺ��̿�����������������ͬ�������첽ʱ�ӵIJ��Ͻ��ж�·ѡ��

��������һ��Ӧ���Ƕ�����ʱ���Ͻ������Ƶ�����²�����������һ���DZ���ƵƵ�ʡ����磬�������������ֻ�ͨѶ�㲥��ʱ�ӡ�

���������õ�Դ��ѹ���ͺ������ƽ��

������������Ҫ��

������Ƶ�źŶ�̬��Χ�㣬ͨ����ֵ�dz����ԣ���ͼ3����ˣ���Ƶ�����������㹻���������֧��������ȡ��ѹ�������ҷ�ֵ���ᱥ�͡�

�������ڵ��͵���ȡ��ѹ����˵�����������ܹ�֧�ַ�ֵ���ʸ߳�ƽ����������15�ֱ������磬���͵�32ŷķ���������ȴ�ԼΪ95�ֱ�������ζ�Ÿö���������95�ֱ���ѹ���������ź�Ϊ1mW��Ϊ�˲�����100�ֱ���ѹ����֧�ֱ�4�е����ָ�������ֵ���ֵ֮��Ϊ15�ֱ�������������������ܹ�֧��115�ֱ���ѹ������Ӧ�ṩ100mW��ֵ���ʡ�����100mW�Ķ�����ʱ����˻�����������ˣ�Ϊ�˳������ʳ�ֵ��������飬��������һ����õ�����ֵ����Ϊ40mW��

ͼ3��������Ƶ�������������

�������������������������� �鿴���� �ظ�

"����Ƶ�������ֲ��28nm���ƶ���ý��оƬϵͳ - ��ģ��� -"���������

��������

- ģ�⼯�ɵ�·�IJ��Լ���-ģ�����-

- ��γ�Ϊ��ɫ��ģ���ʦ:���ָ�����ģ�����-ģ���

- ���ģ�������MEMS��˷��������-ģ�����-

- �����¶ȼƵ�ģ�ⲿ�ֵ�·ͼ-ģ�����-

- �����ⲿ�ж�ʵ��ģ������ݵ��շ�-ģ�����-

- ������/�����̻���ɡ�ģ��뵼��ӭ��ɳ�������-ģ��

- TI�߾���ʵ�������߿γ� �����ɫ����ģ����ƴ���-ģ

- ģ��ʾ����������ʾ����������-ģ�����-

- ������PLC���ڷ�ģ�����������-ģ�����-

- �û���ź�ʾ����̽��ģ��������ź�-ģ�����-