Ladon DSP/SOC����ƽ̨ - ��ģ��� -

Ladon������ϵͳ������ SoC+DSP+Coprocessor �Ľṹ������Ƭ Xilinx ��˾�ĸ����� FPGA ��һƬ ADI ��˾�ĸ߶� DSP оƬΪ�û��ṩ��һ�������ĸ�Ӳ������������

����Ladon�������ṩ�˷ḻ�Ķ���ӿڣ��������������û������������ ADC/DAC ��Ӧ��Ԥ����������չ�ӿڡ�

����

����SoC+DSP+Coprocessor ��ҵ�縴�ӵĸ�����ϵͳͨ�����õĽṹ��ͨ�� Ladon ����������ϵͳ��Ƶ�������ƺ����������Դ����Ʒ��գ����̲�Ʒ����ʱ�䡣

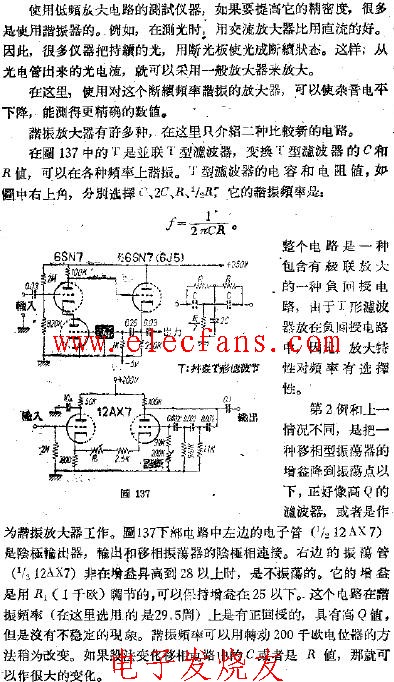

����Ladon ���������һƬ Virtex4-FX60 ��Ϊ SoC ���ƽ̨��һƬ TigerSHARC-TS201S ��Ϊ DSP ���ƽ̨��һƬ Virtex4-SX55 ��Ϊ Coprocessor ���ƽ̨���ɴ�������Ҫ��оƬ��� SoC+DSP+Coprocessor �Ľṹ������ SoC ��Ҫ���ϵͳ�����á�Ӧ�ó���Ͳ���������; DSP оƬ���ϵͳ��Ҫ���еĸ���Ͷ��� DSP �㷨����; Coprocessor ��Ϊ���� DSP �㷨���ٺ������������� SoC �� DSP �� Coprocessor ֮��������������������п��ƺ����ݵĴ��䡣�������� SoC+DSP+Coprocessor �Ľṹ�����������ϵͳ����ƺ���������Ҫ��

����

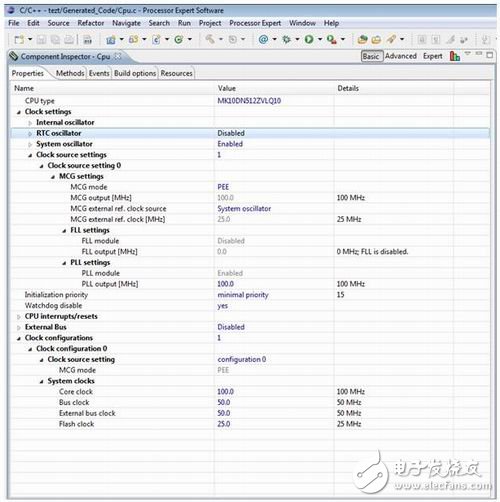

���� ͼ1 Ladon ������ṹ��ͼ

SoC ���ƽ̨

���� ����

����SoC ���ƽ̨������һƬ Xilinx ��˾�� Virtex4-FX60 �� FPGA ���˿� FPGA ��Ϊ Xilinx ��˾�߶�Ƕ��ʽ FPGA ����Ƕ���� PowerPC405 �� CPU �ںˣ���߿������� 450MHz ��֧�� VxWorks �� Linux �� NetBSD �ȶ��ֲ���ϵͳ��

����������Ƕ CPU ���⣬�˿� FPGA �������˷ḻ������Դ�� DSP ���㵥Ԫ���ɽ�������ƺ� DSP �㷨���١�

���� �ؼ����ܵ�

���� FPGA

���� Xilinx XC4VFX60-FF1152 -10C

���� ���� PPC405 �ں�

���� 56880 �� LUT

���� 128 �� 18-bit x 18-bit �˷���

���� 232 �� 18Kb ��Ƕ Block RAM

���� ʱ��

���� 100MHz �� 133MHz �� 60MHz

���� 2 ���û�ʱ���������

���� �洢��

���� 128MB DDR SDRAM ( 32M x 32bits �� ����չ�� 256MB ���� )

���� 64MB FLASH ( 16M x 32bits ������չ 128MB ����)

���� �������ͽӿ�

���� 10/100/1000 RJ-45 ��̫���ӿ�

���� 3 �� USB2.0 �ӿ�(һ�� Host ������ Peripheral )

���� CF �ӿ�

���� PC104 �ӿ�

���� 4 �� RS-232 �ӿ�

���� ADC/DAC ��չ��ӿ�

���� ����

���� 16 �� GPIO

���� 4 ���û� LED

���� 1 �� DDS �����

���� Reset Button

���� DSP ���ƽ̨

���� ����

����DSP ���ƽ̨������һƬ ADI ��˾�� TigerSHARC-TS201S �߶� DSP оƬ����Ϊ Ladon ������������� DSP �����и��������Ķ���������㴦����

���� �ؼ����ܵ�

���� DSP

���� ADI ADSP-TS201SABP-060

���� 600MHz ��Ƶ

���� 24Mb ��Ƕ DRAM

���� 14 �� DMA ͨ��

���� ʱ��

���� 100MHz

���� �洢��

���� 32MB SDRAM ( 4M x 64bits )

���� 4MB FLASH ( 512K x 8bits )

���� Coprocessor ���ƽ̨

���� ����

����Coprocessor ���ƽ̨������һƬ Xilinx ��˾�� 4VSX55 �� FPGA ���˿� FPGA ��Ϊ Xilinx ��˾�ĸ߶������źŴ��� FPGA ����Ƕ�˶�� 512 �� 18-bit x 18-bit �ij˷�������߿������� 500MHz �����и��������Ķ��� DSP ���㡣ʹ������ΪЭ���������ж��� DSP ���㣬�������� DSP оƬ�����㸺����

�ؼ����ܵ�

���� FPGA

���� XC4VSX55-FF1148 -10C

���� 55296 �� LUT

���� 512 �� 18-bit x 18-bit �˷���

���� 384 �� 18Kb ��Ƕ Block RAM

���� ʱ��

���� 100MHz �� 133MHz �� 60MHz

���� 1 ���û�ʱ���������

���� �洢��

���� 128MB DDR SDRAM ( 32M x 32bits �� ����չ�� 256MB ���� )

���� ���� 4MB ZBT SSRAM ( 512K x 64bits )

���� �������ͽӿ�

���� ADC/DAC ��չ��ӿ�

���� ����

���� 4 ���û� LED

���� Reset Button

���� Ŀ��Ӧ��

���� �г�

���� ��ҵ����,����ͨ��,����ͨ��,ҽ�Ƶ���,���»յ���,���ѵ���

���� Ӧ��

���� ���ֵ���,�����źŴ���,ͼ����,����ͨ��

���� �����

���� ����������Ѱ���

���� Ladon ������

���� JTAG ���ص���

���� �������ĵ�

���� �������

���� PC4 ���ص���

���� RS-232 ����

���� 10/100/ 1000M ��̫������

�������������������������� �鿴���� �ظ�

"Ladon DSP/SOC����ƽ̨ - ��ģ��� -"���������

��������

- ģ�⼯�ɵ�·�IJ��Լ���-ģ�����-

- ��γ�Ϊ��ɫ��ģ���ʦ:���ָ�����ģ�����-ģ���

- ���ģ�������MEMS��˷��������-ģ�����-

- �����¶ȼƵ�ģ�ⲿ�ֵ�·ͼ-ģ�����-

- �����ⲿ�ж�ʵ��ģ������ݵ��շ�-ģ�����-

- ������/�����̻���ɡ�ģ��뵼��ӭ��ɳ�������-ģ��

- TI�߾���ʵ�������߿γ� �����ɫ����ģ����ƴ���-ģ

- ģ��ʾ����������ʾ����������-ģ�����-

- ������PLC���ڷ�ģ�����������-ģ�����-

- �û���ź�ʾ����̽��ģ��������ź�-ģ�����-