��ǿ�Ͳ��ж˿�EPP��չ��λ�Ĵ�������ӿڵķ� - ��ģ��� -

��ժ��Ҫ��������EPPЭ����ص㣬Ӧ�ø��ӿɱ����������CPLD����������λ�Ĵ�������ӿڡ�������EPPЭ��ͽӿڵ�Verilog HDL������

�ؼ��ʣ���ǿ�Ͳ��ж˿ڣ�EPP������λ�Ĵ��������CPLD��Verilog HDL

1��������

��������ISA���߲����̨ʽ�������٣�������ʧ��������ϵͳ��Խ��Խ������ò��пڽ������ݴ��͡���ǿ�Ͳ��ж˿�EPP��Enhanced ParallelPort�������봫ͳ�ı����ж˿ڣ�SPP�����ݣ����Ҵ������ʿ��Դﵽ500k��2Mbyte��s���൱��ISA���ߵĴ������ʣ����ر���EPP�ṩ��Ӳ�������źţ�Ϊ��Ӳ������ṩ�˷��㡣��ˣ���ҵ�����л���EPP��Ӧ������㷺��

һЩ������ӡͷ��LED��ʾ�������ȵ���������������ڿ��Ƶ����࣬һ��ʹ����λ�Ĵ����������ݡ������ò���I��O�ڲ�����λ�Ĵ���������ݺ�ͬ�����壬ͨ����Ҫ���I��O��д���ڡ��������һ������EPP���ж˿���չ��λ�Ĵ�������ӿڵķ���������һ��I��O��д�������һ���ֽڵ�������ﵽ���ٴ��͵�Ч����

2��EPP����

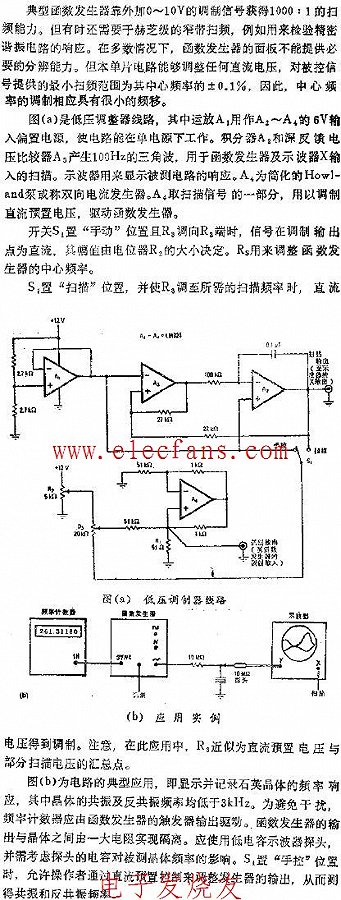

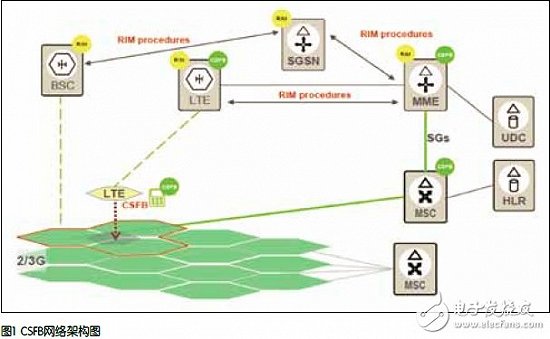

����EPPЭ����IEEE1284�й涨��һ��˫���Ͳ��нӿڣ���������������пڣ�SPP���ļ����ԡ���1��SPP��EPP�����Ŷ��弰�书�ܡ�

����EPP�Ĵ���ռ��8�����ڵ�I��O��ַ�ռ䡣����ַ��0����2��SPP��ͬ���ֱ�ΪSPP�����ݼĴ�����״̬�Ĵ����Ϳ��ƼĴ����������ǽ���I��O�����������EPP��д���ڡ�����ַ��3ΪEPP��ַ�ڣ�����ַ��4ΪEPP���ݿڣ������ǽ���I��O�����Ϳ��Բ���EPP��ַ�����ݵĶ�д���ڡ�

3����λ�Ĵ�������ӿڵ�ʵ��

�������������EPP���п���չ��λ�Ĵ�������ӿڷ�������Ҫ����Wait�����źš�����λ�Ĵ�����λ�����У�����Wait�ź�Ϊ�ͣ���ֹEPP���ڽ�����ʹ��λ�����һ��EPP��������ɡ�����ʹ��һ����������������λ�Ĵ�����λ����֤һ��EPP������ֻ����8����λ�������Է����ݳ�����

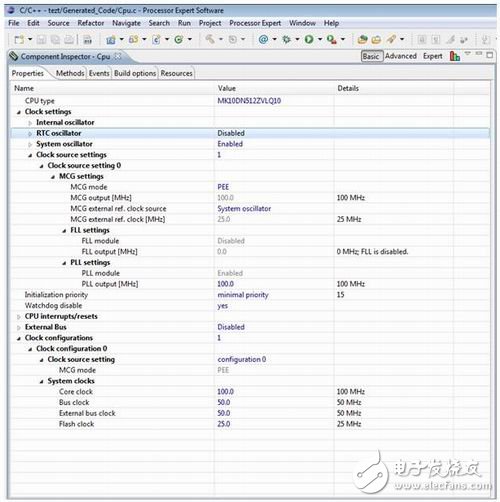

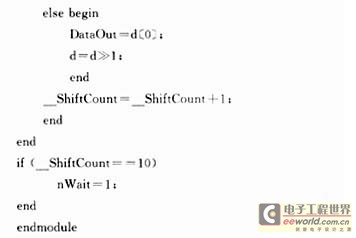

����Ӳ����·ʹ��Altera��˾�ĸ��ӿɱ����������CPLD����ʵ�֡���ṹ��Verilog HDL�������������У�nCsΪƬѡ�źţ��ɵ�ַ�����������ַ��������������ʡ�ԣ���ClkΪ�ⲿʱ��Դ��DataOut��ClkOut�ֱ�Ϊ������ݺ����ͬ�����塣Ϊ��ֹϵͳ��ʱ��ClkӦ�нϸߵ�Ƶ�ʣ���ԼΪ10 MHz���ҡ��ӿڵ�Verilog HDL�������£�

4��������

������EPP���п���չ��λ�Ĵ�������ӿڣ����������EPP�������źţ�������������ʱ����Ҫ����λ�Ĵ�����״̬���в�ѯ��ֻ��Ի���ַ��4�˿ڽ���д�������������һ���ֽڵ���λ�Ĵ������������������̣�ʵ���˸ߵĴ������ʣ��������ʿɴ�8Mbit��s�����Դ�Ϊ��������չ����·������ͨ���Ƚӿڡ�

�����

2������ܵȣ�CPLD��������Ӧ�ã��������������ӿƼ���ѧ�����磬1999

3��J��Bhasker��Verilog HDLӲ���������ԣ���������е��ҵ�����磬2000

�������������������������� �鿴���� �ظ�

"��ǿ�Ͳ��ж˿�EPP��չ��λ�Ĵ�������ӿڵķ� - ��ģ��� -"���������

��������

- ģ�⼯�ɵ�·�IJ��Լ���-ģ�����-

- ��γ�Ϊ��ɫ��ģ���ʦ:���ָ�����ģ�����-ģ���

- ���ģ�������MEMS��˷��������-ģ�����-

- �����¶ȼƵ�ģ�ⲿ�ֵ�·ͼ-ģ�����-

- �����ⲿ�ж�ʵ��ģ������ݵ��շ�-ģ�����-

- ������/�����̻���ɡ�ģ��뵼��ӭ��ɳ�������-ģ��

- TI�߾���ʵ�������߿γ� �����ɫ����ģ����ƴ���-ģ

- ģ��ʾ����������ʾ����������-ģ�����-

- ������PLC���ڷ�ģ�����������-ģ�����-

- �û���ź�ʾ����̽��ģ��������ź�-ģ�����-