�����˽�TI��DSP����оƬTMS320F28335 - ��ģ��� -

��Ϊһ������Ӳ������ʦ����ô���ܶ�DSP��������������һЩͬѧ��DSP��������Ǻܶ࣬����������Ǹ���ҽ���һ��DSP������оƬ������TI��TMS320F28335�����ſ�������һϵ�е����ݣ���һ��DSP�г������˽⡣

�� TMS320F28335��飺

����TMS320F28335����176����LQFP�ı��η�װ���书�ܽṹ�μ��ο����ס�����Ҫ�������£�

���������ܵľ�̬CMOS������ָ������Ϊ6��67 ns����Ƶ��150 MHz��

���������ܵ�32λCPU�������ȸ������㵥Ԫ��FPU�������ù�����ˮ�߽ṹ���ܹ�����ִ���ж���Ӧ��������ͳһ���ڴ����ģʽ������C��C++����ʵ�ָ��ӵ���ѧ�㷨��

����6ͨ����DMA��������

����Ƭ��256 Kxl6��Flash�洢����34 Kxl6��SARAM�洢����1 Kx16 OTPROM��8 Kxl6��Boot ROM������Flash��OTPROM��16 Kxl6��SARAM�������뱣����

��������ʱ��ϵͳ����Ƭ�����������Ź�ģ�飬֧�ֶ�̬PLL���ڣ��ڲ��ɱ�������ͨ������������Ӧ�Ĵ�����ֵ�ı�CPU������ʱ��Ƶ�ʣ�

����8���ⲿ�жϣ����TMS320F281Xϵ�е�DSP����ר�ŵ��ж����š�GPI00~GPI063���ӵ����жϡ�GPI00һGPI031���ӵ�XINTl��XINT2��XNMI�ⲿ�жϣ�GPl032~GPI063���ӵ�XINT3һXINT7�ⲿ�жϣ�

����֧��58�������жϵ������ж���չ��������PIE��������Ƭ��������ⲿ����������ж�����

������ǿ�͵�����ģ�飺18��PWM���������6���߷ֱ�����������ģ�飨HRPWM����6���¼��������룬2ͨ������������ģ�飨QEP����

����3��32λ�Ķ�ʱ������ʱ��0�Ͷ�ʱ��1����һ��Ķ�ʱ������ʱ��0�ӵ�PIEģ�飬��ʱ��1�ӵ��ж�INTl3����ʱ��2����DSP��BIOS��Ƭ��ʵʱϵͳ�����ӵ��ж�INTl4�����ϵͳ��ʹ��DSP��BIOS����ʱ��2������һ�㶨ʱ����

������������Ϊ2ͨ��CANģ�顢3ͨ��SCIģ�顢2��McBSP����ͨ�����崮�нӿڣ�ģ�顢1��SPIģ�顢1��I2C���Ӽ��ݵĴ������߽ӿ�ģ�飻

����12λ��A��Dת��������16��ת��ͨ����2�����������������ⲿ�ο���ѹ��ת���ٶ�Ϊ80 ns��ͬʱ֧�ֶ�ͨ��ת����

����88���ɱ�̵ĸ���GPIO���ţ�

��������ģʽ��

����1��9 V�ںˣ�3��3 V I��O���磻

��������IEEEll49��1����Ƭ��ɨ�����ӿڣ�JTAG����TMS320F28335�Ĵ洢��ӳ����ע�����¼��㣺

����Ƭ������Ĵ�����0~3ֻ���������ݴ洢�����û������ڸô洢����д�����

����OTP ROM����0x38 0000~0x38 03FF��Ϊֻ���ռ䣬�洢A/Dת������У�����û����ܶԴ˿ռ�д�����

������ʹ��Ӧ��eCANģ�飬ҲӦʹ��ʱ��ģ�飬��ΪeCAN�����RAM�ռ�����һ��RAM��

����������ð�ȫ���룬�洢������Ox33FF80~0x33FFF5��ȫ��д������0x0000�����������ڴ洢��������ݡ���֮��0x33FF80~Ox33FEF���Դ洢���ݻ��������0x33FFF0~Ox33FFF5ֻ�ܴ洢���ݡ�

�������湤�ߺͿ���������

����TMS320F28335���������У������Ż�C��C++���룯��࣯��������CCS���ɿ����������������XDS510������������CCS��һ�������Ѻã��������Ƶļ��ɵĿ���ƽ̨�����б༭����ࡢ���롢��Ӳ��������Թ��ܡ�

����TMS320F28335 ��ADC��

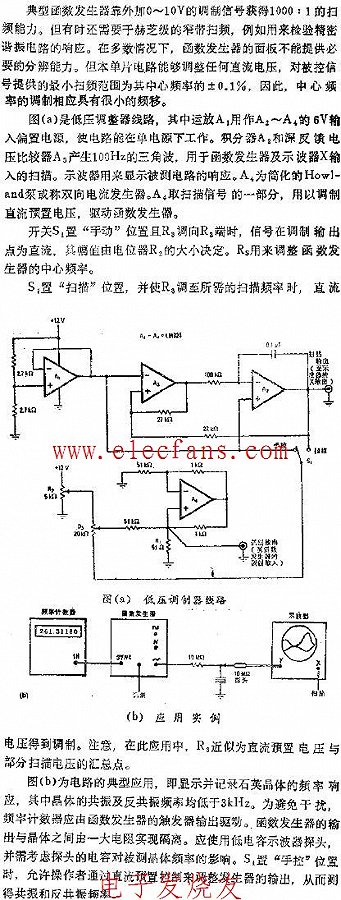

����TMS320F28335����16ͨ����12λ��ģ��ת����ADC�������Ա�����Ϊ����������8ͨ������ģʽ��Ҳ����ͨ������AdcRegs.ADCTRL1.bit.SEQ_CASC=1����������Ϊһ��16ͨ���ļ�������ģʽ������ķ�ʽ����ͨ������ AdcRegs.ADCTRL1.bit.ACQ_PS=1����������Ϊ˳��ɼ������ӵ�ͨ����ʼ����ͨ�������� ֵ��ע�����Ƭ��ADC�������ѹ��ΧΪ0--3V��һ������3V��Ƭ�ϵ�ADCģ�齫�ᱻ�յ���TI�ϵ�DATASHEET������ADC�ľ��ȿɴﵽ12λ��ʵ���ϴﵽ���ˡ������ԣ����ǹ�����õ�ʱ����Դﵽ11λ�Ͳ����ˡ���������������һ��ADCģ���ԭ����������ֵ�����湫˾�����㣬���й�ʽ�е�3ΪƬ�ڲο���ѹDigital Value=4096*��Input Analog Voltage-ADCLO��/3 ����when 0 V �� input �� 3 V����ADC���Է�ΪSEQ1��SEQ2����ģ�飬����SEQ1����ADCIN00--ADCIN07��SEQ2����ADCIN08--ADCIN15��SEQ1ģ�����ͨ��������PWM���ⲿ�ж���������������SEQ2������ͨ���ⲿ�ж��������������������ADC������DMA�������ݽ�����

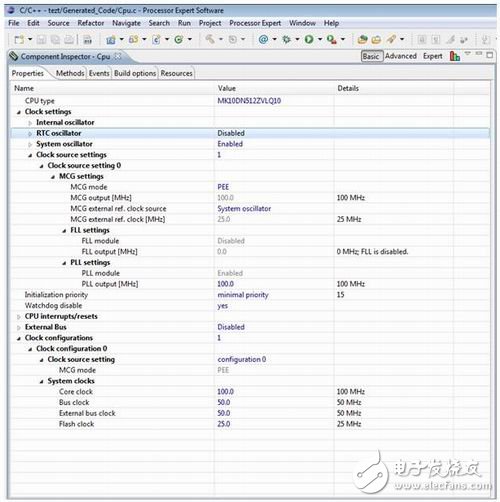

TMS320F28335 ��ʱ�ӽ��ܣ�

����TMS320F28335����һ������PLL��·��Ƭ��ʱ��ģ�飬ΪCPU�������ṩʱ�������ַ�ʽ��һ�������ⲿ��ʱ��Դ���������ӵ�X1�����ϻ���XCLKIN�����ϣ�X2�ӵأ���һ����ʹ����������ʱ�ӣ���30MHz�ľ��������20PF�ĵ�����ɵĵ�·�ֱ����ӵ�X1��X2�����ϣ�XCLKIN���Žӵء����dz��õڶ���������ʱ�ӡ���ʱ�ӽ�ͨ��һ���ڲ�PLL�����·�����б�Ƶ������F28335�������Ƶ����150M�����Ա�Ƶֵ�����5�����б�Ƶֵ��PLLCR�ĵ���λ��PLLSTS�ĵ�7��8λ������������ϸ�ı�Ƶֵ���Բ���TMS320F28335��Datasheet��������F28335��ʱ�����ã�

����void InitPll��Uint16 val�� Uint16 divsel��

����{

����// Make sure the PLL is not running in limp mode

����if ��SysCtrlRegs.PLLSTS.bit.MCLKSTS ��= 0��

����{

����// Missing external clock has been detected

����// Replace this line with a call to an appropriate

����// SystemShutdown����; function.

����asm���� ESTOP0����;

����}

����// DIVSEL MUST be 0 before PLLCR can be changed from

����// 0x0000. It is set to 0 by an external reset XRSn

����// This puts us in 1/4

����if ��SysCtrlRegs.PLLSTS.bit.DIVSEL ��= 0��

����{

����EALLOW;

����SysCtrlRegs.PLLSTS.bit.DIVSEL = 0;

����EDIS;

����}

����// Change the PLLCR

����if ��SysCtrlRegs.PLLCR.bit.DIV ��= val��

����{

����EALLOW;

����// Before setting PLLCR turn off missing clock detect logic

����SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1;

����SysCtrlRegs.PLLCR.bit.DIV = val;

����EDIS;

����// Optional�� Wait for PLL to lock.

����// During this time the CPU will switch to OSCCLK/2 until

����// the PLL is stable. Once the PLL is stable the CPU will

����// switch to the new PLL value.

����//

����// This time-to-lock is monitored by a PLL lock counter.

����//

����// Code is not required to sit and wait for the PLL to lock.

����// However�� if the code does anything that is timing critical��

����// and requires the correct clock be locked�� then it is best to

����// wait until this switching has completed.

����// Wait for the PLL lock bit to be set.

����// The watchdog should be disabled before this loop�� or fed within

����// the loop via ServiceDog������

����// Uncomment to disable the watchdog

����DisableDog����;

����while��SysCtrlRegs.PLLSTS.bit.PLLLOCKS ��= 1��

����{

����// Uncomment to service the watchdog

����// ServiceDog����;

����}

����EALLOW;

����SysCtrlRegs.PLLSTS.bit.MCLKOFF = 0;

����EDIS;

����}

����// If switching to 1/2

����if����divsel == 1��||��divsel == 2����

����{

����EALLOW;

����SysCtrlRegs.PLLSTS.bit.DIVSEL = divsel;

����EDIS;

����}

����// If switching to 1/1

����// * First go to 1/2 and let the power settle

����// The time required will depend on the system�� this is only an example

����// * Then switch to 1/1

����if��divsel == 3��

����{

����EALLOW;

����SysCtrlRegs.PLLSTS.bit.DIVSEL = 2;

����DELAY_US��50L��;

����SysCtrlRegs.PLLSTS.bit.DIVSEL = 3;

����EDIS;

����}

����}

TMS320F28335 ���ⲿ�ж��ܽ

��������������Ҫʮ�����DSP���ж�ϵͳ��C28XXһ����16���ж�Դ��������2���������ε��ж�RESET��NMI����ʱ��1�Ͷ�ʱ��2�ֱ�ʹ���ж�13��14����������12���ж϶�ֱ�����ӵ������ж���չģ��PIE�ϡ�˵�ļ�һ�����PIEͨ��12������28335�˵�12���ж�����������PIE������һ����12*8���߷ֱ����ӵ����裬��AD��SPI��EXINT�ȵȡ�����PIE������12*8=96���ⲿ�жϡ���12����ж���28335�˵��жϼĴ���IER�����ƣ���IERȷ��ÿ���жϵ���������һ����жϣ���IER |= M_INT12;˵������Ҫ�õ�12����жϣ����ǵ�12�������ʲô�ж�CPU����֪����Ҫ����PIEIERȷ�� ��������������PIEģ���еļĴ���PIEIER�еĵ�8ȷ�����ж�����һ��ĵڼ����жϣ���Щ���ö�Ҫ����CPU�����Dz�������PIEIER����12�ܼ���PIEIER1-PIEIER12�������⣬PIEģ�黹���жϱ�־�Ĵ���PIEIFR��ͬ�����ĵ�8λ�������ⲿ�жϵ�8����־λ��ͬ��CPU��IFR�Ĵ������ж���ı�־�Ĵ������ɴ˿�����CPU�������жϼĴ�������12����жϣ�PIE�������жϼĴ�������ÿ����8�����жϡ�����֮�⣬�����õ���һ���ⲿ�жϣ���Ӧ�Ļ����ⲿ�жϵļĴ�������Ҫע��ľ����ⲿ�жϵı�־Ҫ�Լ�ͨ�����������㡣��PIE��CPU���жϱ�־�Ĵ�����Ӳ�������㡣

����EALLOW; // This is needed to write to EALLOW protected registers

����PieVectTable.XINT2 = &ISRExint; //�����ж���ڵ�ַ

����EDIS; // This is needed to disable write to EALLOW protected registers

����PieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enable the PIE blockʹ��PIE

����PieCtrlRegs.PIEIER1.bit.INTx5= 1; //ʹ�ܵ�һ���е��ж�5

����IER |= M_INT1; // Enable CPU ��һ���ж�

����EINT; // Enable Global interrupt INTM

����ERTM; // Enable Global realtime interrupt DBGM

����Ҳ����˵��12���е�ÿ���ж϶�Ҫ����������ͬ���ã�ʣ�µIJ���ȥ�����Լ����жϡ��������ᵽ��EXINT�������������͵�ƽ���Ǿͽ���

�����жϣ�������ǵij���������Ҫ����һ�£�DSP��GPIO�ڶ���������Ϊ�ⲿ�жϿڣ������÷������£�

����GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 0; //ѡ��������GPIO��

����GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 0;

����GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 0;

����GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 0;

����GpioCtrlRegs.GPBDIR.bit.GPIO54 = 0;//ѡ�����Ƕ��������

����GpioCtrlRegs.GPBDIR.bit.GPIO55 = 0;

����GpioCtrlRegs.GPBDIR.bit.GPIO56 = 0;

����GpioCtrlRegs.GPBDIR.bit.GPIO57 = 0;

����GpioCtrlRegs.GPBQSEL2.bit.GPIO54= 0;//GPIOʱ�Ӻ�ϵͳʱ��һ����֧��GPIO

����GpioCtrlRegs.GPBQSEL2.bit.GPIO55= 0;

GpioCtrl

�������������������������� �鿴���� �ظ�

"�����˽�TI��DSP����оƬTMS320F28335 - ��ģ��� -"���������

��������

- ģ�⼯�ɵ�·�IJ��Լ���-ģ�����-

- ��γ�Ϊ��ɫ��ģ���ʦ:���ָ�����ģ�����-ģ���

- ���ģ�������MEMS��˷��������-ģ�����-

- �����¶ȼƵ�ģ�ⲿ�ֵ�·ͼ-ģ�����-

- �����ⲿ�ж�ʵ��ģ������ݵ��շ�-ģ�����-

- ������/�����̻���ɡ�ģ��뵼��ӭ��ɳ�������-ģ��

- TI�߾���ʵ�������߿γ� �����ɫ����ģ����ƴ���-ģ

- ģ��ʾ����������ʾ����������-ģ�����-

- ������PLC���ڷ�ģ�����������-ģ�����-

- �û���ź�ʾ����̽��ģ��������ź�-ģ�����-