FPGA与CF卡的接口设计 -

[导读]1 前言

CF卡是目前应用最为广泛的存储卡,由于它不带驱动器,也没有其它的移动部件,因此,极少出现机械故障,使存储的图像数据更加安全。CF卡的使用寿命也非常长,即使用上 100多年也可以保证数据完好无损。而且

1 前言

CF卡是目前应用最为广泛的存储卡,由于它不带驱动器,也没有其它的移动部件,因此,极少出现机械故障,使存储的图像数据更加安全。CF卡的使用寿命也非常长,即使用上 100多年也可以保证数据完好无损。而且 CF卡耗电量小,只有普通硬盘的 5%。与其它存储卡相比,容量大是 CF卡的另一个优势,目前主流产品已经达到 512Mb和 1Gb标准。另外它还具备速度快、价格便宜等优点。

最近几年,FPGA[1]以其应用的灵活方便蓬勃发展,在通信、航空航天、医疗设备、消费类电子产品等领域一展身手。使用 FPGA控制 CF的技术到目前为止还没有成熟,本文从硬件和软件角度出发,介绍了 FPGA与 CF卡的接口设计、给出了用 Verilog HDL语言编写的读取 CF卡中数据的源程序并给出了用双 RAM访问 CF卡的编程技巧。

本文引用地址: http://www.21ic.com/app/eda/200908/46171.htm

2 系统设计

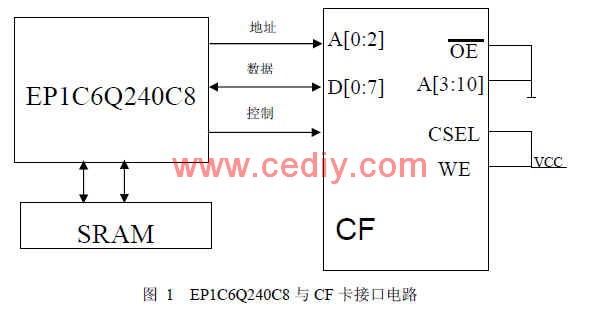

系统采用 EP1C6Q240C8[2]为主控制芯片,它是 Altera公司开发的一款 Cyclone系列的FPGA芯片。它有丰富的 I/O接口、PLL和内部存储资源,无需外接 SRAM,既节约成本又简化了设计过程。

系统采用 Kingston公司生产的 CF卡,容量为 1Gb。

2.1 系统硬件设计 [3][4]

CF卡的访问方式有三种,分别为 I/O模式、 Memory模式和 TrueIDE模式。本系统采用 TrueIDE模式访问 CF卡。需要注意的是当主机电源一直接通时,拔插 CF卡将会使其从原来的 TrueIDE方式重新配置成 Memory方式。所以要让 CF卡一直工作在 TrueIDE模式,需要在电源加电启动时将 OE输人信号接地。此方式也支持 8位存取方式。

当 CSEL输入信号接地时, CF卡工作方式为主模式;CSEL输入信号接高电平时,CF卡工作方式为从模式。本系统中将 CF卡配置成从模式工作方式。当采用 TrueIDE访问模式工作时,第 3位到第 10位地址线需要接地, WE信号需要接高电平。

2.2 系统软件设计

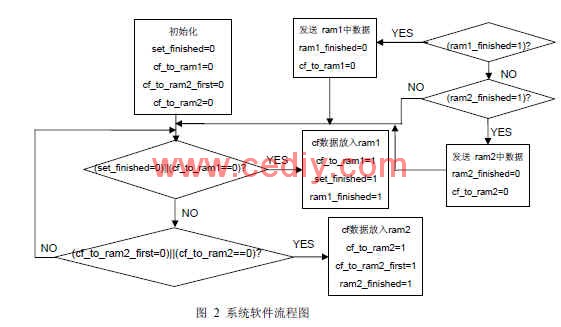

CF卡的数据存储以扇区为基本单位。系统读写 CF卡时都是以扇区为单位进行的。为了满足系统对速度和控制连续性的要求,系统的程序设计中,利用 FPGA的内部资源开辟了两块 RAM,用于存储一个扇区的数据,这样从 CF卡读数据到 RAM和将 RAM中的数据读到被控系统中就成了两个相对独立的工作过程,这样既利用了 CF卡大容量的存储特性又利用了 EP1C6Q240C8的工作速度快和内部资源丰富的优点。图 2是利用双 RAM的具体程序设计的流程图。

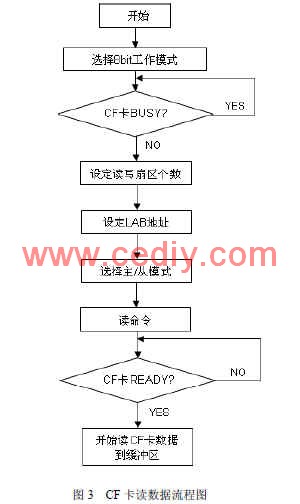

3 CF卡读数据

从 CF卡读取一个扇区的数据,如图 3所示。首先根据表 1所示的控制命令设定 8位工作模式、设置读取的扇区数目、相应地址和访问模式;然后发送读命令(0x20),等待 CF卡准备就绪后,从数据寄存器中连续读取一个扇区的数据放入到数据缓冲区。

4 CF卡读数据源程序

由于篇幅限制,这里仅给出部分程序。

always @(posedge clk or negedge reset)

begin if((set_finished==0)||((cf_to_ram1)&(ram1_finished==0))||((cf_to_ram2)& (ram2_finished==0))||((cf_to_ram2_first)&(ram2_finished==0)))

begin if(time_cont <= 166) begin

time_cont <= time_cont +1; end else begin

time_cont <= 0; end

end if(time_cont == 26) begin

ceaddr <= `features_wr ; write_data <= `features_data; write_start <= 1;

end if(time_cont == 28) begin

iowr <= 0; end if(time_cont == 34) begin

iowr <= 1; end if(time_cont == 35) begin

ceaddr <= 5'b11111; write_start <= 0; end

end

5 结束语

本设计采用 FPGA读写 CF卡,既利用了 FPGA的内部资源丰富和设计方便的优点,同时利用了 CF卡容量大、体积小和价格低廉等优点,给出了高效读写 CF卡的方法,该方法已成功应用于实际系统中。

查看评论 回复