����CPLD������������������Ƶ����� -

[����]0 ���ԡ���������ϵͳ�����,���ݲ�ͬ�������Ҫ,����������ż����Ƶ��������Ƶ����������Ƶ��,�еĻ�Ҫ���ռ�ձȡ��ڻ���cpld�����ӿɱ����������������ϵͳ�����,������ʵ���ɼ��������伶�����ɸ�����ʽ��ż

0 ����

�������õ�ַ: http://www.21ic.com/app/eda/200908/45998.htm

����������ϵͳ�����,���ݲ�ͬ�������Ҫ,����������ż����Ƶ��������Ƶ����������Ƶ��,�еĻ�Ҫ���ռ�ձȡ��ڻ���cpld�����ӿɱ����������������ϵͳ�����,������ʵ���ɼ��������伶�����ɸ�����ʽ��ż����Ƶ���ǵ�ռ�ձȵ�������Ƶ,���Ե�ռ�ձȵ�������Ƶ����������Ƶ��ʵ�ֽ�Ϊ���ѡ�

������������vhdl�������ټ��ɵ�·Ӳ���������ԣ�,ͨ��quartus �� 4.2����ƽ̨,�����һ���ܹ�ʵ�ֵ�ռ�ձȵ������ͽ��Ƶ�ռ�ձȵİ�������Ƶ��,������Ʒ���ԭ����,����ֻ����ٵ�cpld���굥Ԫ��

����1 ���ԭ��

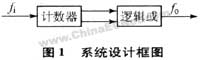

����ϵͳ��ƿ�ͼ��ͼ1��ʾ��

�������ݲ�ͬ��Ƶϵ�������ʵ��ļ���������,ÿ������ֵ��Ӧ����ʱ���ź�fi��һ������,��q0ֻ��fi�������ؼ��ʵ��ļ�����Χ�ڲ����ߵ�ƽ,���q0��q1�����������,�����õ�����ķ�Ƶ�ź�fo��q1����������������Ƶ�в����½��ش����ʱ������,ʹ���ռ�ձ�,�Լ��ڰ�������Ƶ��,��ʱ���½��ش�������Ƶ�źŵ�������,��ʵ�ְ�������Ƶ��

��������������ȷ�������������Լ�q0��q1�����ߵ�ƽ���ʱ���Եļ�����Χ��Ϊ��������,�ֹ涨���±�ǣ���Ƶϵ��Ϊdivide��max downto 0��,����max�Ƿ�Ƶ����Ӧ�������������λ,���ڰ�������Ƶ,���λ����0λΪС��λ;q 0_count��q1_count�ֱ�Ϊq0��q1�����ߵ�ƽ�ļ�����Χ,����divide��max downto 1��Ϊa,divide��max downto 2��Ϊb,divide��max downto 0����1Ϊc��

����1.1 ż����������Ƶ

�������������ڶ�Ϊ0��c����ռ�ձȵ�ż����Ƶ������ʵ��,�ڴ˲�����������������Ƶ,ֻ�赱q0_count��aʱq0����ߵ�ƽ,��q1_count��a��1ʱq1���һ�����ڵĸߵ�ƽ,���������q0��q1��Ϊ�͵�ƽ,Ȼ���q0��q1����,���õ����fo��������Ļ�����Ƶʱ���źš�

����1.2 ��������Ƶ

��������������Ϊ0��c���������������ż��,ֻ�赱q0_count��bʱq0����ߵ�ƽ,��b��q1_count��a��bʱq1����ߵ�ƽ,���������,q0��q1��Ϊ�͵�ƽ;�����������������,ֻ�赱q0_coun��bʱq0����ߵ�ƽ,��b��q1_count��a��b����ߵ�ƽ,���������q0��q1��Ϊ�͵�ƽ,Ȼ���q0��q1�����������f0������İ�������Ƶʱ���źš�

����2 ��������Ӳ����·����

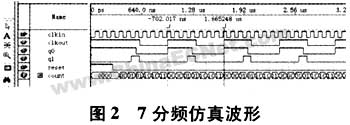

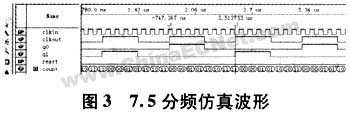

�������������ԭ��,����quartus �� 4.2������7��Ƶ��7.5��Ƶ�ķ��沨����ͼ2��ͼ3��ʾ��

����ֻҪ���ij���,����ʵ�����������Ͱ�������Ƶ��

�����������altera��˾��epm7064slc84��10���ɵ�һ�����ݲɼ�ϵͳ����ͨ��,�������á�

����3 ������

��������Ƶ����ԭ����,����һ����ͨ����,����ʹ�õ�cpld���굥Ԫ������,����epm7064��,��������������Ƶ����ֻ��7�����굥Ԫ��

�������������������������� �鿴���� �ظ�

"����CPLD������������������Ƶ����� -"���������

��������

- Xilinx FPGA�ڻ���������е����� - FPGA/ASIC���� -

- ����CPU���ģ������д

- ����FPGAоƬ�Ĺ��£���֪�������أ� - �ɱ���� -

- Mellanox����Ƕ��Xilinx FPGA,��ʵ�����繦������ -

- ��˼�Ƽ���������Cortex-A76��Mali-G76���������ڵ�Ar

- ����˼�뵼���Ƴ�ȫ�µ�ģ�黯IP�ˣ���Ϊ�ͻ��ṩ����

- FPGA��Ʒ��������������˼����ս�����������г����� -

- ����FPGA�����ѧϰ�Ĺ�ϵ̽����� - �ɱ���� -

- ���ΪAI�����ޣ�������FPGAΪ����֧�� - �ɱ����

- SDSoc��������-ʹ��MIO����LED - �ɱ���� -