基于FPGA的Viterbi译码器设计 -

[导读]摘要:卷积码及其Viterbi译码是现代通信系统中常用的一种信道编码方法。文中介绍了Viterbi译码算法的原理,分析了Viterbi译码器的结构,然后用Verilog语言设计了一种基于Altera公司的EP3C120F780C8芯片的(2,l,7)Vi

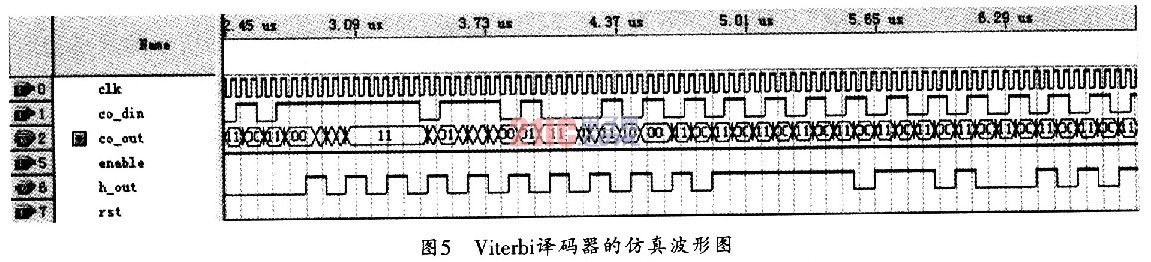

摘要:卷积码及其Viterbi译码是现代通信系统中常用的一种信道编码方法。文中介绍了Viterbi译码算法的原理,分析了Viterbi译码器的结构,然后用Verilog语言设计了一种基于Altera公司的EP3C120F780C8芯片的(2,l,7)Viterbi译码器,同时给出了时序仿真图。

关键词:卷积码;Virelbi译码;FPGA

本文引用地址: http://www.21ic.com/app/eda/201006/60561.htm

0 引言

在现代通信系统中,要使信号能够更可靠地在信道中传输,往往需要我们在信道编码中采用纠错码来降低信号受噪声的影响,以降低传输的误码率。这种方法叫做差错控制编码或纠错编码,其思想是在发送端的信息码元序列中增加一些监督码元,这些监督码与信码之间有一定的关系,接收端可以利用这种关系由信道译码器来发现或纠正错误的码元。

1 卷积码

前向纠错(FEC)是目前常用的一种差错控制方法,在这种方法中,发送端发送能够被纠错的码,接收端则在收到这些码后,通过纠错译码器来发现其中的错误并自动纠正接收码字中的错误。在前向纠错方法中,卷积码及其Viterbi译码是常用的信道编码方案。

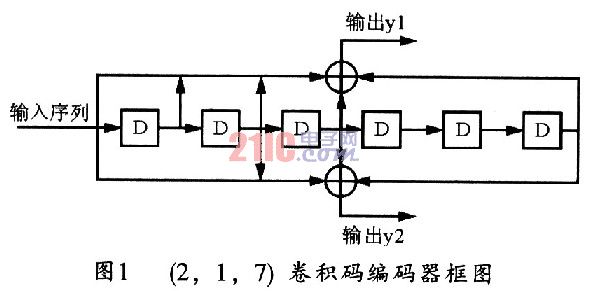

卷积码通常用(n,k,N)表示,其中n为输出信息比特,k为输入信息比特,N为约束长度,卷积码的编码效率为Rc=k/n,图1所示为(2,l,7)卷积码的编码器框图。

(2,1,7)卷积码编码器由6个延时器(图l中的D模块,可用寄存器实现)和两个模二加法器组成,它的编码约束度为7,码率为1/2。即输入端输入1比特信息,输出端输出2比特编码信息,并分为上、下两路并行输出。

2 Viterbi译码器原理

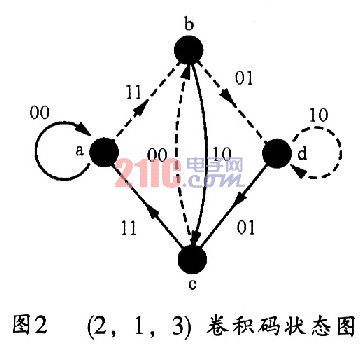

近年来,维特比算法具有很大的发展,目前在数字通信的前向纠错系统中用的较多。Viterbi译码的基本原理是把已接收到的序列与所有可能的发送序列进行比较,选择其中码距最小的一个序列作为发送序列。下面以(2,1,3)卷积码编码器的编出码为例,来说明Viterbi解码的方法和过程。图2所示是该码的状态图。

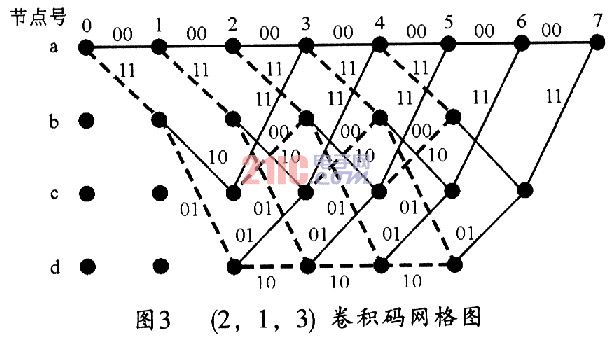

结合状态图可得出如图3所示的状态与时间关系图,称为网格图。该图设输入信息数目L=5,所以画有L+N=8个时间单位(节点),图3中分别标以0至7。设编译器从a状态开始运作。该网格图的每一条路径都对应着不同的输入信息序列。由于所有的可能输入信息序列共有2KL个,因而其网格图中所有可能的路径也是2KL条。

设编译器送出的码序列为C,经过离散无记忆信道传输后送入译码器的是序列R,E是信道错误序列,则有:R=C+E。译码器根据接收序列R,可以按最大似然估计准则来找出编码器在网格图上所走过的路径,这个过程就是译码器计算、寻找的最大似然函数:

经计算可得,上式等价于寻找与R有最小汉明距离的路径,即寻找:

对于二进制输入且Q进制输出的离散无记忆信道,实际上就是寻找与R有最小软距离的路径,而此时的度量就是软判决距离:

式中,Rs与Cjs是接收序列R与Cj序列的Q进制表示。

Viterbi算法是一种基于最大似然估计的算法。它并不是在网格图上一次比较所有可能的2kl条路径(序列),而是接收一段,就计算、比较、选择一段最可能的码段(分支),从而使整个码序列达到一个有最大似然函数的序列。

3 Viterbi译码器的结构

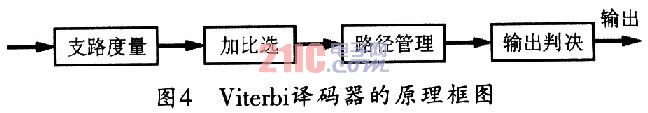

由以上分析可以得出如图4所示的Viterbi译码器的原理框图。

由图4可见,Viterbi译码器大致可以分为四个部分:支路度量模块(BMU)、加比选模块(ACS)、幸存路径管理模块(SMU)和输出产生模块。其中支路度量模块用于完成译码器输入信号与网格图上的可能路径信号的分支度量计算;加比选模块主要把前一个状态的路径度量与当前输入信号的分支度量相加,以得到该分支的路径度量,然后比较不同分支路径度量的大小,同时找出最小的度量值,并更新该状态的度量值,最后输出状态转移信息;路径管理模块可对加比选单元输出的状态转移信息进行处理,以便为输出判决做准备。输出模块可根据幸存路径管理单元的输出进行输出判决,最后输出译码信息。

4 Viterbi译码器的FPGA实现

本文所设计的(2,1,7)Viterbi译码器可在Altera公司的QuartusII8.0开发环境下进行设计,并在QuartusII下进行仿真。首先利用编码器对已知的序列进行编码,产生这个输入序列的编码码字,并对产生的编码码字进行人为加扰,用以验证所设计的Viterbi译码器对错误信息的纠错能力。图5所示是该译码器的仿真图,对于图5,通过对比原始编码序列和译码器输出的序列,可以看出。输入的序列与译码输出的序列一致,故可证明Vitervi译码器设计的正确性。

5 结束语

本文通过在QuartusII8.0下对基于EPGA芯片EP3C120F780C8进行Viterbi译码器进行了设计与验证。结果表明,本设计中的Viterbi译码器能够正确地进行译码输出。

查看评论 回复

"基于FPGA的Viterbi译码器设计 -"的相关文章

- 上一篇:如何从SCH转变到PCB -

- 下一篇:基于FPGA的LDPC编码设计 -