基于IEEE802.16e标准的LDPC编码器设计与实现 -

[导读]

摘要:根据IEEE802.16e标准中对LDPC码的定义,利用FPGA对编码器进行了实现。所采用的算法使用了线性复杂度编码,降低了逻辑资源占用量,并提高了编码速度。

本文引用地址: http://www.21ic.com/app/eda/201807/798131.htm

1962年Gallager在对纠错编码的研究中提出了LDPC码,但是由于当时的硬件条件不足,直到90年代末随着超大规模集成电路的推广才真正为人们所重视。虽然在高斯信道中LDPC(Low Density Parity Check,低密度奇偶校验码)码相比其他编码方法具有更优良的性能,但是由于其逼近香农限的性能是在较长的码长情况下才能得到体现,使得实现起来具有相当大的复杂度,即便是当今的超大规模集成电路也很难直接实现较长码长的编码和解码。于是如何构造和改进LDPC码成为目前研究的热点,而准循环低密度奇偶校验码的发现,为LDPC编译码的硬件实现提供了可能。QC—LDPC码具有更好的结构性与随机性,在保证码的信道性能不变的前提下,极大的简化了编码和译码电路,是目前实现LDPC编译码器的主流算法。正是由于这些优势,LDPC码已被WIMAX(IEEE802.16e)、WLAN(IEEE802.11n)、DVB-T等标准选定为信道编码的备选编码,并且极有可能成为第四代无线通信的编码标准。

1 IEEE802.16e标准中对LDPC码的规定

IEEE802.16e标准中LDPC码的校验矩阵为

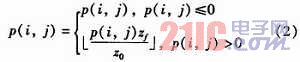

其中,Pij被定义为z×z的单位变换矩阵或零矩阵,单位变换矩阵是通过对单位矩阵循环右移得到的。LDPC码是由的效验矩阵日定义,其中m是校验位的长度,n是码长的长度。基本矩阵中的移位集{p(i,j)}是用来决定相同码率不同码长的移位大小,对于码率1/2、3/4A、3/4B、2/3B和5/6的各种码,p(i,J)p(i,j)由式(2)决定。

其中,[x]表

查看评论 回复

"基于IEEE802.16e标准的LDPC编码器设计与实现 -"的相关文章

- 上一篇:浅谈高纵横比多层板电镀技术 -

- 下一篇:DIP双列直插式封装简介 -