放大电路的负反馈详细解析 - 参考设计 -

放大电路负反馈的特点

一、提高放大倍数的稳定性

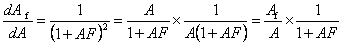

引入负反馈以后,放大电路放大倍数稳定性的提高通常用相对变化量来衡量。

因为:

![]()

所以求导得:

即:

![]()

二、减小非线性失真和抑制噪声

由于电路中存在非线性器件,会导致输出波形产生一定的非线性失真。如果在放大电路中引入负反馈后,其非线性失真就可以减小。

需要指出的是:负反馈只能减小放大电路自身产生的非线性失真,而对输入信号的非线性失真,负反馈是无能为力的。

放大电路的噪声是由放大电路中各元器件内部载流子不规则的热运动引起的。而干扰来自于外界因素的影响,如高压电网、 雷电等的影响。负反馈的引入可以减小噪声和干扰,但输出端的信号也将按同样规律减小,结果输出端的信号与噪声的比值(称为信噪比)并没有提高。

三、负反馈对输入电阻的影响

由于负反馈可以提高放大倍数的稳定性,所以引入负反馈后,在低频区和高频区放大倍数的下降程度将减小,从而使通频带展宽。

引入负反馈后,可使通频带展宽约(1+AF)倍。

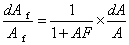

四、负反馈对输入电阻的影响

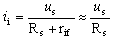

(a)串联反馈 (b)并联反馈

图1 求输入电阻

1、串联负反馈使输入电阻提高

引入串联负反馈后,输入电阻可以提高(1+AF)倍。即:

![]()

![]()

式中:ri为开环输入电阻

rif为闭环输入电阻

2、并连负反馈使输入电阻减小引入并联负反馈后,输入电阻减小为开环输入电阻的1/(1+AF )倍。

即:

![]()

![]()

五、负反馈对输出电阻的影响

1、电压负反馈使输出电阻减小

放大电路引入电压负反馈后,输出电压的稳定性提高了,即电路具有恒压特性。

引入电压负反馈后,输出电阻rof减小到原来的1/(1+AF)倍。

2、电流负反馈使输出电阻增大

放大电路引入电流负反馈后,输出电流的稳定性提高了,即电路具有恒流特性。

引入电流负反馈后,使输出电阻rof增大到原来的(1+AF)倍。

3、负反馈选取的原则

(1)要稳定静态工作点,应引入直流负反馈。

(2)要改善交流性能,应引入交流负反馈。

(3)要稳定输出电压,应引入电压负反馈;

要稳定输出电流,应引入电流负反馈。

(4)要提高输入电阻,应引入串联负反馈;

要减小输入电阻,应引入并联负反馈。

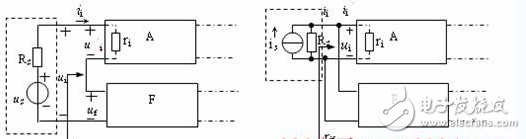

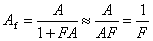

六、 深度负反馈的特点

1、串联负反馈的估算条件

反馈深度(1+AF)》》1的负反馈,称为深度负反馈。通常,只要是多级负反馈放大电路,都可以认为是深度负反馈。

.此时有:

![]()

因为:

![]()

![]()

所以: xi≈xf

估算条件:

(1)对于深度串联负反馈有:ui≈uf (称之为“虚短” )

(2)由于串联负反馈的闭环输入电阻增大,在深度负反馈条件下:ii≈0(称之为“虚断” )

2、并联负反馈的估算条件

因为深度负反馈有:xi≈xf

(1)对于深度并联负反馈有:ii≈if(或称之为“虚断”)

(2)并联负反馈的闭环输入电阻减小,在深度负反馈条件下: ui ≈0 (称之为“虚短” )

七、深度负反馈放大倍数的估算

例1 估算图2所示反馈放大电路的电压放大倍数Auf。

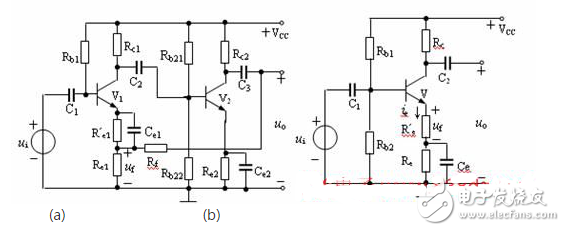

(a) (b)

图2 电压串联负反馈电路和电流串联负反馈电路

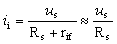

解:(1)在图2(a)所示放大电路中,可以判断Rf构成越级电压串联负反馈,因而可认为是深度负反馈,即有ui≈uf。。因而其反馈系数为:

![]()

所以闭环电压放大倍数为:

![]()

![]()

另外,从电路结构上可以认为,反馈电压是输出电压经电阻Rf和Re1串联分压后得到的,所以:

![]()

![]()

仍可得:

![]()

![]()

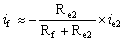

(2)在图2(b)所示放大电路中,可以判断

![]()

构成电流串联负反馈。所以在深度负反馈条件下,有ui≈uf。因为uf= ie&TImes;

![]()

,uo=-io&TImes;Rc≈ie&TImes;Rc,所以其反馈系数为:

![]()

![]()

所以闭环电压放大倍数为:![]()

![]()

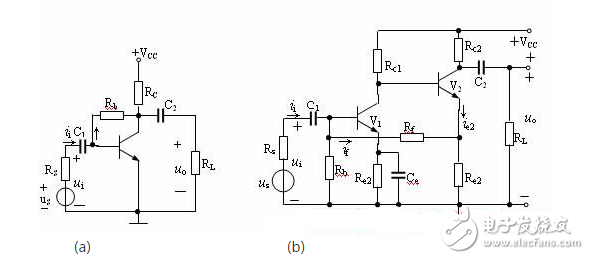

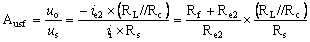

例2 估算图3所示反馈放大电路的源电压放大倍数Ausf。

(a) (b)

图3 电压并联负反馈电路和电流并联负反馈电路

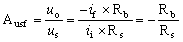

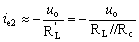

解:(1)在图3(a)所示放大电路中,Rb构成电压并联负反馈。在深度负反馈条件下,由式(4—16)可知ii≈if( 或——虚断),而且还有ui≈0(虚短)。

或——虚断),而且还有ui≈0(虚短)。

由图3(a)的输入回路可得:![]()

所以,闭环源电压放大倍数为:

(2)在图3(b)所示放大电路中,Rf构成越级电压并联负反馈。在深度负反馈条件下,ii≈if(虚断),并且有ui≈0(虚短),所以有:

又从图3(b)的输出端可知:

所以闭环源电压放大倍数为:

从以上分析过程可以看到,在深度负反馈条件下,放大倍数仅由一些电阻来决定,几乎与放大电路无关。若不是深度负反馈,则用上述方法计算出来的结果误差较大,此时应采用其他方法分析。