Incisive 12.2版本融入Cadence验证IP,SoC验证效率提高50% - PLD

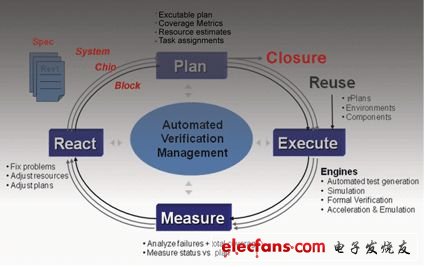

全球电子设计创新领先企业Cadence设计系统公司(NASDAQ: CDNS),今天公布了一个新版的尖端功能验证平台与方法学,拥有全套最新增强功能,与之前发布的版本相比,可将SoC验证效率提高一倍。 Incisive ®12.2提供了两倍性能,全新Incisive调试分析器产品,全新低功耗建模,以及当今复杂IP与SoC高效验证所需的数百种其他功能。

对于IP block-to-chip验证,增强的内容包括:

• 仿真引擎的性能倍增

• 通过最近推出的Incisive调试分析器提升调试功能

• 自动寄存器验证应用只需一次形式分析运行即可取代数百次的功能测试

• 用最新Incisive Metrics Center功能简化覆盖数据分析

在SoC层面,Incisive 12.2对于更长时间的运行仿真有着更大的容量,包括那些融合了低功耗和混合信号的设计。

对于SoC验证,增强的内容包括:

• 仿真器中改良的低功耗算法,对于elaboraTIon的时间可实现性能两倍提升。这种最新Incisive技术可精确建模低功耗设计中关电与恢复的场景。

• 综合的数字中心型混合信号解决方案使用真实数据模型(RNM),实现使用wreal或SystemVerilog-RNM的仿真速度提升300多倍。

• Palladium XP仿真加速中支持了加速模块与toggle覆盖率,将测试时间从几个小时缩短到几分钟。

Gnodal Ltd.计划在2013年应用Incisive 12.2版本, 其创始人兼首席技术官Fred Homewood表示:“性能、灵活性与高效率是我们高密度开关的特点,Incisive平台与支持团队赋予了这些质量,让我们能够大大提升我们的 Incisive Enterprise Simulator licenses,并采用Incisive Enterprise Manager和Incisive SimVision调试。我们正在采用指标驱动的验证方法学,并将使用其自动验证规划功能,向我们的客户展示我们的开发效率。”

“我们的一些客户在高级节点上建造了2亿门级SoC,甚至更大。”Cadence硅实现部门高级副总裁Chi-Ping Hsu说,“这些设计的成功验证是至关重要的,需要分散在世界各地团队的配合。Incisive 12.2的技术涵盖面之广是无可匹敌的,为这些团队实现了所需的效率提升,让他们的设计更快、更高质量地投放市场。”

全新Incisive版本融入了Cadence®验证IP,用于SoC验证,还有用于系统验证的Cadence Virtual System Platform,以及用于加速的Palladium® XP,它能在软件型仿真和硬件型加速之间进行热转换。

查看评论 回复