Altera或为其FPGA产品采用全耗尽型SOI技术? - PLD新闻 -

电子发烧友网讯【翻译/Triquinne】:伦敦消息,Altera一位高级工程师对全耗尽型SOI(FDSOI)芯片制造过程进行评估,并得出以下结论:对FPGA而言,该技术(全耗尽型SOI技术)有着特殊的用处。这无形中增加了未来Altera考虑换掉台积电(TSMC)代工厂或采取增加代工厂策略的可能性。

在旧金山举行的国际电子设备大会举行的全耗尽型SOI研讨会上,Altera资深技术研究员Jeff Watt提出在FPGA中采用14nm全耗尽技术。

据报道,Altera由于2013年的滑坡,所以一直忙于跟TSMC合作开发20nm平面式CMOS节点,但是却也很担心该节点是否会出现功耗很高(power hungry)的问题。

格勒诺布尔研究所实验室、SOI晶片生产商Soitec和 IBM已经和意法半导体(ST)合理开发FDSOI进程【详见:意法半导体(ST)与Soitec携手CMP提供28纳米FD-SOI CMOS制程】。此外,ST也成为了Globalfoundries公司的新客户,进而提升其生产能力。一直以来,台积电在FDSOI方面并不出色,但是也指出将计划在2014年的下一代技术中迅速向16nm FinFET制造工艺转变。

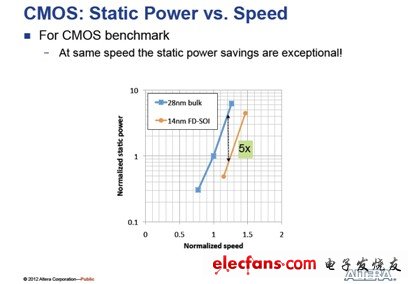

Jeff Watt在演讲中对 28nm Bulk平面CMOS工艺和14nm FDSOI平面CMOS进行了对比。这预示着Jeff Watt已经接受了这个惯例:28nm之后的下一代FDSOI节点有可能是14nm FDSOI工艺。

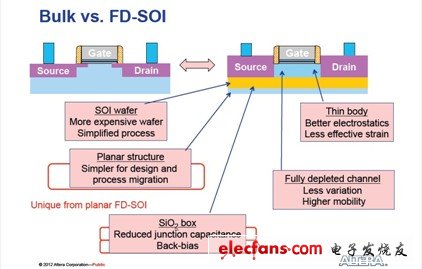

图 Bulk CMOS工艺和FDSOI CMOS工艺对比图

Jeff Watt说,相比28nm Bulk平面CMOS工艺而言,14nm FDSOI在同样的切换功率下性能可以提高35%,在相同的延迟时间下切换功率要低32%。

图 Bulk CMOS工艺和FDSOI CMOS动态功率及速度对比

图 Bulk CMOS工艺和FDSOI CMOS静态功率及速度对比

查看评论 回复