Verilog HDL语言的文件调用问题:include使用方法介绍 - HDL语言

来源: 网络用户发布,如有版权联系网管删除 2018-08-11

电子发烧友网讯:Verilog中可以使用预处理命令 `include “文件名” 来包含新文件。`include “文件名”的位置需要在 module声明之后。

这里举个例子便于大家理解,param.h存放了参数LENTH,顶层mult.v使用了它。

mult.v代码如下

1 module mult (

2 input clk,

3 input rst,

4 input [LENTH-1:0] A,

5 input [LENTH-1:0] B,

6 output [LENTH-1:0] C

7 );

8

9 `include “param.h”

10

11 reg [LENTH-1:0] c_reg;

12

13 always@(posedge clk or negedge rst)

14 if(rst == 1‘b0)begin

15 c_reg <= 32’b0;

16 end

17 else begin

18 c_reg <= A*B;

19 end

20

21 assign C = c_reg;

22

23 endmodule24

param.h代码如下

1 parameter LENTH = 32;

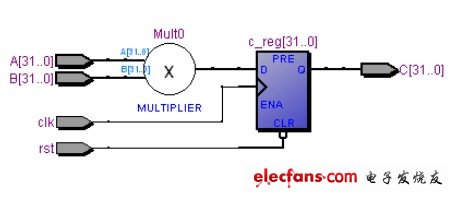

综合之后RTL图

查看评论 回复