CPLD与FPGA的发展与应用之对比 - FPGA/ASIC技术 -

可编程逻辑器件(ProgrammableLogicDevice,PLD)给数字系统的设计带来了革命性的变化。他的影响丝毫不亚于20世纪70年代单片机的发明和使用,可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路。使用PLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。PLD的这些优点使得PLD技术在20世纪90年代以后得到飞速的发展,成为电子设计领域中最具活力和发展前途的一项技术。

目前,这项技术PLD按其内部结构不同又延伸出两个分支,即复杂可编程逻辑器件(ComplexProgrammableLogicDevice,CPLD)和现场可编程门阵列(FieldProgram-mableGateArray,FPGA),两者统称为可编程逻辑器件或CPLD/FPGA。

1 PLD发展过程

早期的可编程逻辑器件只有可编程只读存贮器(PROM)、紫外线可擦除只读存贮器(EPROM)和电可擦除只读存贮器(E2PROM)三种。由于结构的限制,他们只能完成简单的数字逻辑功能。

稍后,出现了一类结构上稍复杂的可编程芯片,即可编程逻辑器件(PLD),他能够完成各种数字逻辑功能。这一阶段(大约20世纪70年代中期)的产品主要有可编程阵列逻辑(ProgrammableArrayLogic,PAL),PAL由一个可编程的“与”平面和一个固定的“或”平面构成,或门的输出可以通过触发器有选择地被置为寄存状态。PAL器件是现场可编程的,他的实现工艺有反熔丝技术、EPROM技术和E2PROM技术。

20世纪80年代初期,在PAL的基础上,又发展了一种通用阵列逻辑(GenericArrayLogic,GAL),他采用E2PROM工艺,实现了电可按除、电可改写,其输出结构是可编程的逻辑宏单元,因而他的设计具有很强的灵活性,至今仍有许多人使用。

20世纪80年代中期,为了弥补上述缺陷,又先后推出了可擦除、可编程的逻辑器件(ErasableProgrammableLogicDevice,EPLD)。CPLD和FPGA,EPLD的集成度更高,设计更灵活,但内部连线功能较弱。

2 结构比较

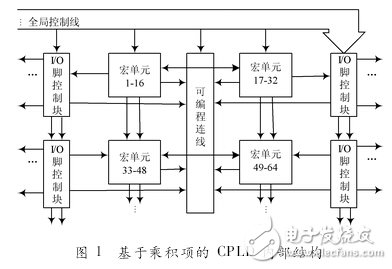

不同厂家对PLD的叫法不尽相同,但一般来说,把基于乘积项技术,FLASH(类似E2PROM工艺)工艺的PLD叫CPLD;把基于查找表技术,SRAM工艺,要外挂配置E2PROM的PLD叫FPGA。下面从内部结构对2者进行比较。

查看评论 回复