基于555流水灯电路的设计与实现 - FPGA/ASIC技术 -

1.引言

繁华的都市,当夜幕降临时,五缤纷的彩灯灯便亮了起来,点亮这个黑暗的世界,给人民生活增添一点情趣,而流水灯是其中的角色之一。随着技术的不断发展,控制彩灯的电路不断更新,这里主要介绍由555定时器构成的流水灯控制电路。

2.555定时器

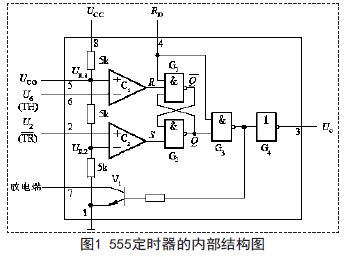

2.1 555定时器的内部结构(如图1所示):

(1)分压器

①5脚悬空时。

②5脚外接控制电压时。

(2)电压比较器

电压比较器C1和C2是两个结构完全相同的理想运算放大器。比较器有两个输入端,分别用1和0表示相应输入端上所加的电压,用表示比较器的比较结果(1代表高电平,0代表低电平)。

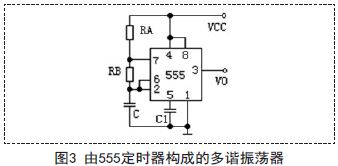

(3)基本RS触发器

(4)放电三极管

V1是一个集电极开路的放电三极管。当时,V1导通;当时,V1截止。

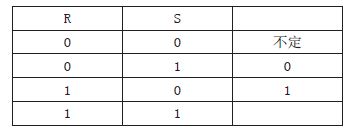

2.2 555定时器功能表(如图2所示)

555定时器功能表基本说明了555定时器的功能。

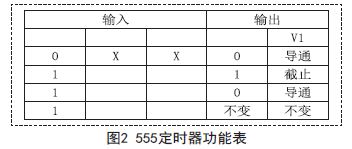

2.3 555定时器组成的多谐振荡器

由555定时器构成的多谐振荡器如图3所示,RA,RB和C是外接定时元件,电路中将高电平触发端(6脚)和低电平触发端(2脚)并接后接到RB和 C的连接处,将放电端(7脚)接到RA,RB的连接处。由于接通电源瞬间,电容C来不及充电,电容器两端电压为低电平,小于(1/3)Vcc,故高电平触发端与低电平触发端均为低电平,输出为高电平,放电管V1截止。这时,电源经RA,RB对电容C充电,使电压按指数规律上升,当上升到(2/3)Vcc 时,输出为低电平,放电管V1导通,把从(1/3)Vcc上升到(2/3)Vcc由于放电管V1导通,电容C通过电阻RB和放电管放电,电路进人第二暂稳态,其维持时间的长短与电容的放电时间有关,随着C的放电,下降,当下降到(1/3)Vcc时,输出为高电平,放电管V1截止,Vcc再次对电容C充电, 电路又翻转到第一暂稳态。

查看评论 回复