一种基于ARM+FPGA的高精度数据采集系统设计 - FPGA/ASIC技术 -

1、引言

随着图像处理、工业控制、无线通信等领域的飞速发展,对数据采集系统的速度、精度等性能要求也越来越高。这些要求都对数据采集系统的设计和实现提出了新的挑战。目前数据采集系统的设计方案通常分为以下几类:

1)以微处理器单一控制芯片和A/D转换器形式为主,该设计方案简单,在对性能要求不高的应用场合为了降低成本甚至可以采用集成A/D转换器的微处理器。

2)采用通用计算机配置数据采集卡的方式,通常需要开发计算机端应用程序,可以完成复杂的计算,但不同的采集卡相应的驱动程序不同,如果需求改变需要更换采集卡时,相应的应用程序也需要重新开发。因此,该设计方案通用性差,实时性不高。

3)以ARM和FPGA或DSP和FPGA组合方式作为采集系统的核心,ARM处理器适合控制领域,DSP处理器适合信号处理领域,FPGA器件由于其自身特点,适合高速并行采集与处理领域,具有ARM或者DSP等处理器无法比拟的优势。这类组合方式结合各自特点,处理能力强,应用范围广。

ARM和FPGA之间的数据交换采用双口RAM芯片来实现FIFO功能。系统中ARM处理器作为系统控制核心,负责控制整个系统工作时序、并将数据通过网络上传到服务器中进行存储。FPGA负责A/D转换器的模式配置,数据传输。该组合方式结合ARM在控制方面和FPGA在采集方面的优势,具有通用性强、配置灵活的特点。

2、系统设计

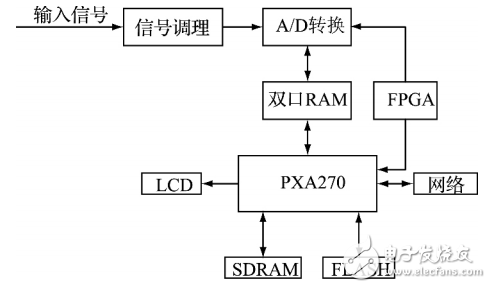

本系统硬件主要由信号调理电路、模数转换器ADS1278、FPGA器件CyCLOnE系列EP1C6、双口RAMIDT7205和处理器PXA270及外围电路组成,系统结构框图如图1所示。输入信号经过信号调理电路后,进入A/D转换器进行数据转换,将模拟信号转换成23位尾数和一符号位的数据,FPGA配置A/D转换器并将转换的数据按照顺序存储到双口RAM中,当转换数据存储满后中断ARM处理器,ARM处理器将数据从双口RAM读出进行运算,并通过网络接口将采集数据传输到服务器。

图1 系统结构

2.1、24位A/D转换芯片ADS1278

ADS1278是德州仪器(TI)公司推出的采样率高达128KS/S、24位8通道同步采样Σ-ΔADC。支持多种工作模式,内部集成线性相位数字滤波器,数据输出接口支持SPI或可选帧同步,便于与FPGA互连。可满足国防、航天和医疗应用。

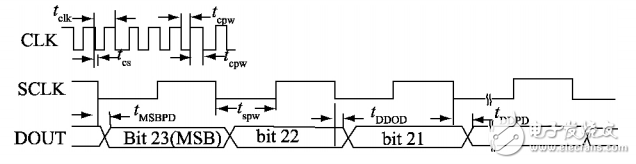

ADS1278转换器内部集成的数字滤波器通过奈奎斯特采样将输入信号抽取为长度为1比特的高分辨率数字信号。8通道输入信号分别进入独立的8个A/D转换器,它内部由高阶斩波器、数字滤波器、调制器组成,可将输入模拟信号经过高阶滤波器后得到数字信号。图2为ADS1278的SPI格式下,时钟和数据时序图。

图2 SPI格式下时序

查看评论 回复