ucos iii在zynq上的移植 - FPGA/ASIC技术 -

本教程介绍了如何使用μC/ OS BSP建立在ZYNQ基本应用程序®使用Vivado -7000 ™ IDE和赛灵思® SDK。在本教程中,您将使用Vivado IP集成器配置ZYNQ处理器系统以及FPGA架构集成软外设。然后,您将使用μC/ OS BSP来生成使用一个基本的应用程序μC/ OS-III实时内核。

教程将让您体验以下概念:

一个μC/ OS-III的应用程序和BSP的生成

BSP和驱动程序配置

选择和使用赛灵思独立驱动和Micrium的自定义驱动程序

标准输出(文字痕迹)

中断处理

本教程是不是意味着作为Vivado设计流程的演示。读者建议先通过官方赛灵思教程和文档尝试本教程之前。

软件要求

合适的Vivado设计套件是本教程所需。是否支持您的主板WebPACK的版本都可以使用。

在μC/ OS BSP。BSP是随μC/ OS-III的评估目的的完整的源代码。请参阅安装说明进行安装。

Vivado设计套件2014.3版本在本教程中使用。截图和设计步骤可能会有所不同在其他版本。

硬件要求

本教程的编写和赛灵思ZC702,安富利ZedBoard测试™和MicroZed ™。然而,大多数如果不是全部基于ZYNQ开发平台应该是适合本教程。为了达到最佳效果董事会应该有一个可用的UART输出连接到PS UART。

确保你有适当的调试器或调试电缆连接,并且板载跳线进行相应配置。

硬件设计

在写任何赛灵思可编程器件的软件应用程序是创建硬件设计首先需要。本教程的目的是建立一个硬件设计具有下列组件。

的Cortex-A9处理器,硬化

经由处理器系统的UART标准输出

基本FPGA设计

AXI互连连接到PS通用AXI4主端口

两个软AXI定时器

这两个定时器到PS的路由

步骤1.调用Vivado IDE和创建项目

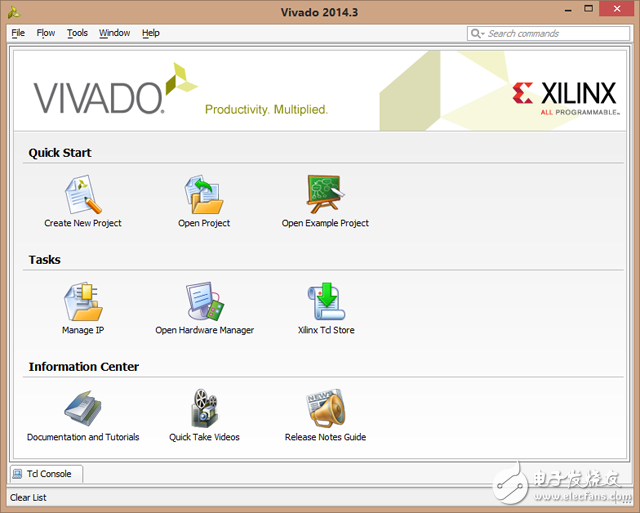

1.打开Vivado IDE作为起始页。

图 - Vivado起始页

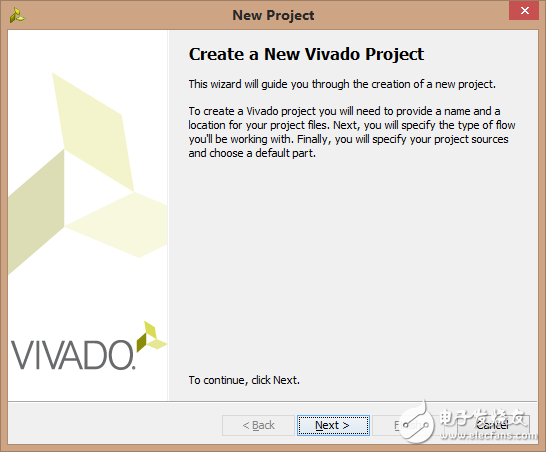

2.从入门页面中点击“创建新项目”。这应该打开新项目向导。 图- Vivado新建项目向导点击下一步。

图 - Vivado新建项目向导

3.输入项目名称和位置。确保“创建项目的子目录”被选中。点击下一步。

4.选择“RTL工程”作为项目类型,并检查“不要指定此时来源”复选框。点击下一步。

5.在默认部分对话框中选择你板或部分。点击下一步。

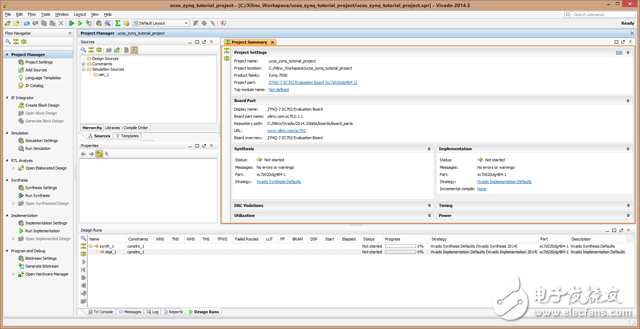

6.在项目摘要页面单击Finish。

这应该在一个空白的项目主要Vivado IDE项目视图为您带来。

图 - Vivado项目视图

步骤2.创建一个IP集成器设计

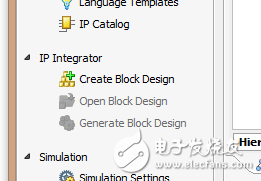

1.在流动导航器中选择“创建模块设计”项目

图 - 模块化设计流程的项目

2.指定块设计一个名称,然后单击确定。

第3步:添加和设置ZYNQ处理器系统的IP块

1.通过右键单击程序框图画布,选择“添加IP ......”添加IP对话框。

图 - 添加IP上下文菜单

2.在搜索字段中键入“ZYNQ”,然后选择ZYNQ7处理系统,最后按回车键的ZYNQ IP模块添加到设计

图 - 添加IP ZYNQ

您现在应该看到ZYNQ块单独的程序段设计原理图的中间。

图 - 座ZYNQ

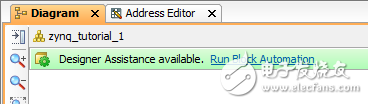

3.调用的ZYNQ块自动化对话框。这应该高亮显示为绿色的画布上,并可以通过点击“运行座自动化”启动。 图- ZYNQ座自动化援助

座自动化为Zynq7处理系统将只可当Vivado知道你正在使用的电路板。

图 - ZYNQ座自动化援助

4.在“运行座自动化”对话框中选择“应用预设董事会”,并留下了交叉触发设置为禁用 。点击OK。

图 - ZYNQ座自动化对话

如果一切顺利阻止自动化应该连接外部存储器和固定的I / O自动。

图 - ZYNQ座自动化结果

查看评论 回复