东芝和产综研为解决电压驱动型MRAM重要课题开辟道路-embedcc资讯

东芝和日本产业技术综合研究所自旋电子学研究中心的研究小组开发出了可降低电压驱动型非易失性磁内存“电压扭矩MRAM”的写入误码率的新写入方式。将在“IEDM 2016”上发表。

这种内存与原来的电流驱动型STT-MRAM相比,特点是写入电流小,容易降低耗电量。但目前写入时误码率高,是实用化面临的一个重要课题。此次新开发的写入方式能够成为解决这一课题的手段。

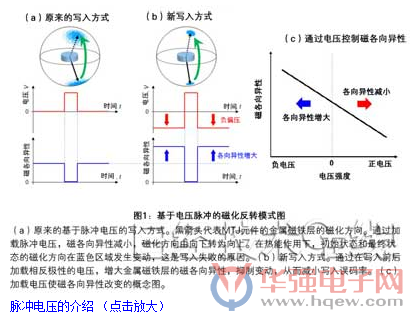

顾名思义,电压驱动型MRAM就是加载脉冲电压,使存储单元(MTJ元件)的磁化发生反转,从而写入信息。这时,如果加载负偏压且是脉冲宽度在1ns以下的高速脉冲电压,就有利于降低写入误码率。

不过,原来的磁内存用写入电路,布线的充放电需要时间,因此很难加载脉冲宽度在1ns以下且波形漂亮的脉冲电压。

设计了专用电路

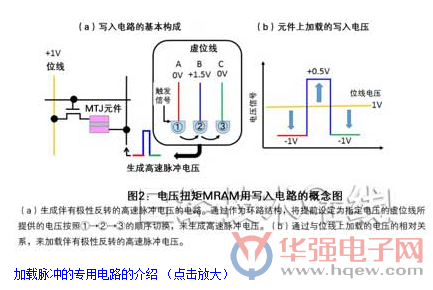

为此,研发人员此次设计了生成高速脉冲电压的专用电路。具体就是,在位线之外,准备了三根(A、B、C)事先加载了低电压或高电压的“虚位线”。比如,A和C加载0V电压,B加载+1.5V电压。收到写入命令(触发信号)后,按照A、B、C的顺序依次快速开放切换虚位线,可以生成幅1.5V的高速脉冲电压。实际上,MTJ元件上加载的电压会与位线的加载电压形成压差。如果位线的加载电压为+1V,A开放时形成的压差为-1V,B开放时(写入时)形成的压差为+0.5V,C开放时形成的压差为-1V。

这时,A开放时,读取写入前的记录信息,如果不需要写入信息,通过跳过写入程序,就可以提高写入速度。另外,C开放时,也就是在写入后对记录信息进行再次确认,以判断是否出现了错误。如果出现了错误,则再次写入同一信息。

根据实际制作的直径30nm的MTJ元件的实测数据,利用CMOS电路模拟器执行上述写入程序进行验证,结果发现,写入误码率改善了1~2位数。过去,东芝和产综研的研究小组曾实现10-3左右的误码率。如果使用这次的方式,可以改善到10-5至10-4左右。如果在一次写入程序中可实现10-5左右的误码率,通过反复写入2~3次,就可以实现10-15左右至10-10左右的低误码率,达到实用水平。写入2~3次虽然要多花一些时间,但能将写入速度控制在靠近主存储器的“末级缓存”所需要的10ns左右。

查看评论 回复

"东芝和产综研为解决电压驱动型MRAM重要课题开辟道路-embedcc资讯"的相关文章

热门文章

- 我国提交PCT国际专利申请量跃居全球第二-embedcc资讯-

- GaN Systems公司与罗姆联手致力于GaN功率器件的普及-e

- TI为智能音箱和回音壁提供优质音效与综合保护-embedcc

- ADI公司针对下一代射频、微波和毫米波应用 推出行业最

- 以高集成度为核心:新型MSP430微控制器 为感测应用提

- Molex发布下一代数据中心解决方案 以满足不断增长的带

- 新日本无线为IoT电子器件推出具有宽带、超低功耗的运

- ADI公司隔离式电源转换器支持B类系统EMI等级-embedcc

- PI现可提供已通过汽车级AEC-Q100认证的SCALE-iDriver

- 聚焦智慧视频,Socionext推出升级版混合编解码器-embe