台积电制程工艺快人一步 投250亿美元生产5nm 预计2年后问世 -

[导读]7nm之外,台积电也准备5nm多时了,根据他们在半导体技术论坛所说,台积电将投资250亿美元发展5nm工艺,预计2019年试产,2020年量产。

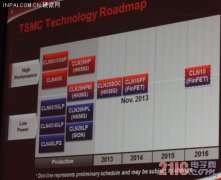

摩尔定律问世50年多来一直指导着半导体行业的发展,但在10nm节点之后普遍认为摩尔定律将会失效,制程工艺升级越来越难。今年台积电、三星及Globalfoundries将把制程工艺推进到7nm。下一个节点是5nm,台积电在上周的半导体技术论坛上宣布将投资250亿美元研发、生产5nm工艺,预计2020年问世。

本文引用地址: http://www.21ic.com/news/mcu/201806/787392.htm

台积电今年的重点是7nm工艺,之前已经报道过多次了,目前台积电的7nm工艺已经有50多个芯片已经或者正在流片中,苹果A12、海思麒麟980及高通骁龙855芯片以及NVIDAI、AMD新一代GPU芯片都会采用台积电的7nm工艺。

与16nm FF工艺相比,台积电的7nm工艺(代号N7)将提升35%的性能,降低65%的能耗,同时晶体管密度是之前的三倍。2019年初则会推出EUV工艺的7nm+(代号N7+)工艺,晶体管密度再提升20%,功耗降低10%,不能性能没有变化。

7nm之外,台积电也准备5nm多时了,根据他们在半导体技术论坛所说,台积电将投资250亿美元发展5nm工艺,预计2019年试产,2020年量产。

根据之前的资料,与初代7nm工艺相比,台积电的5nm工艺大概能再降低20%的能耗,晶体管密度再高1.8倍,至于性能,预计能提升15%,不过使用新设备的话可能会提升25%。从这里预估的数据来看,制程工艺到了5nm之后,性能或者能效提升都会放慢,而制造难度也越来越高,投资高达数百亿美元,这也导致了未来的5nm芯片成本非常贵。

目前开发10nm芯片的成本超过了1.7亿美元,7nm芯片则要3亿美元左右,5nm芯片研发预计成本超过5亿美元,而开发28nm工艺芯片只要数千万美元,这一趋势将导致未来的5nm芯片客户越来越少,未来只有苹果等少数资本雄厚的公司才会坚持升级制程工艺了。

5nm工艺之后还会有3nm工艺,此前只有三星公布了3nm工艺的路线图,在这个节点上三星将改用GAA晶体管,FinFET晶体管在5nm之后将逐渐被放弃,厂商们需要开发新的晶体管架构,GAA就是其中之一。

查看评论 回复