单片机控制的动态数据缓存器的DRAM读/写控制过程 -

来源: 网络用户发布,如有版权联系网管删除 2018-09-06

[导读]

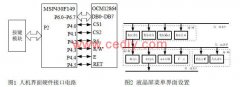

读取一字节数据的程序段如下: 读取数据时,T1先置1,其后的RD信号将行地址送到地址线AB上,并使D。触发器锁存Tl,Q,变成低电平,使RAS有效(低电平),实现行选通;再置TO为l,其后的RD信号

读取一字节数据的程序段如下:

本文引用地址: http://www.21ic.com/app/mcu/201805/760884.htm

读取数据时,T1先置1,其后的RD信号将行地址送到地址线AB上,并使D。触发器锁存Tl,Q,变成低电平,使RAS有效(低电平),实现行选通;再置TO为l,其后的RD信号将列地址送到AB上,并产生CAS信号,使欲读出单元的数据出现在DB上。RD失效的上升沿使CAS失效,同时,D2触发器置1,使D1清零,RAS也失效变为高电平。经过RC延迟放电,使欲读出单元的数据出现在DB上,D2重新清零,Q2又为高电平,恢复初始状态D1、D2均为零。

程序最后送T0、T1低电平,封锁RAS和CAS,防止系统中其他读/写器动作使DRAM产生误动作。

写数据过程与此类似。

查看评论 回复