单片机控制的动态数据缓存器的控制电路 -

来源: 网络用户发布,如有版权联系网管删除 2018-09-06

[导读]

由于单片机具有功能强,使用灵活,体积小,性价比高等特点,近年来在测控系统中得到广泛应用。而在许多场合,单片机作为下位机,担负着控制数据测量、采集和向上位机传送的任务,也即起着收集、缓冲

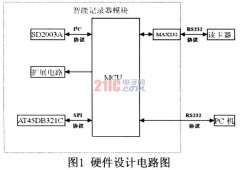

由于单片机具有功能强,使用灵活,体积小,性价比高等特点,近年来在测控系统中得到广泛应用。而在许多场合,单片机作为下位机,担负着控制数据测量、采集和向上位机传送的任务,也即起着收集、缓冲和存储数据的作用。动态存储器DRAM具有容量大,价格低的特点,适合于数据量比较大的单片机应用系统;但其不足之处在于,必须在规定的时间范围内进行定时刷新。本节介绍一种单片机控制的动态数据缓存器,通过合理设计软硬件,即可实现对DRAM的控制,特别适合性价比高的单片机系统。

控制电路

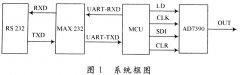

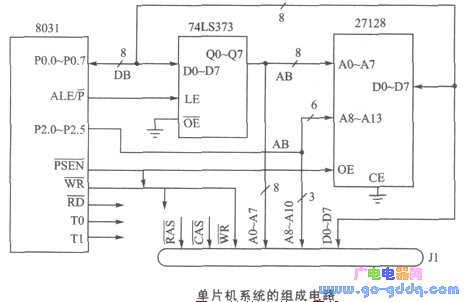

为了便于说明,给出单片机系统的部分组成电路,如图1所示。单片机采用51系列的8031,外扩16 KB的EPROM,动态存储器采用1 MB的微机内存,Jl为其插座及其各引脚信号。1 MB的动态存储器行、列地址各用10位,即用10根地址线A0~A9。

本文引用地址: http://www.21ic.com/app/mcu/201805/760883.htm

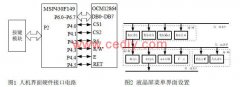

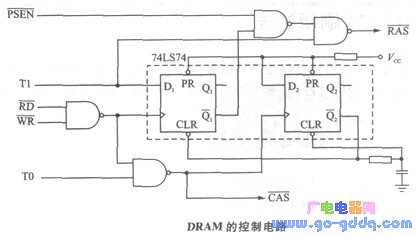

DRAM的控制电路如图2所示。其核心为一正沿触发双D触发器74LS74,由8031和TO、Tl、PSEN和EN、WR信号控制其工作状态。读/写数据时,TO、Tl置高电平;刷新DRAM时,TO置1,PSEN有效;当T0、T1都置0时,行、列选通关闭,禁止对DRAM读/写操作。

查看评论 回复