【正天伟课堂】PCB孔破漏测原因

欢迎进入正天伟课堂,本期通过对孔破电测漏出到客户端的原因进行分析,从而对电测孔破漏测问题提出改善的方向和方法。

一、 前言

线路板制造过程中,经过多个生产工序,生产过程中难免存在一些功能性的缺陷。电测试作为开、短路测试是一种极为重要的功能测试方法。PCB产品出货前一般进行100%电子测试,甚至有些厂家针对特别客户的产品进行200%测试,即进行交叉测试,分不同机,不同人测试。在这种严格的测试下,仍有不少企业会出现孔破不良品,流出到客户端,直至客户组装后才发现PCB开路不良,或者阻值偏高,造成了产品报废,导致赔偿损失,甚至客户流失。那么为什么会出现孔破的不良品流出至下游组装工序,本文就其原因进行分析,并提出一些改善方向和方法。

二、电测漏出原因分析

1.人为漏失

A.员工责任不明确,没有品质意识,工作不认真,员工操作失误,把问题板错放到PASS区。针对此问题,增加警报装置,即员工放错位置,就响警报,现在已经成为标配。

B. 区域划分不清楚。PASS板、待修理板、待测板的摆放区域,需统一规划,标识要清晰。用框盛放生产板必须要有颜色区分。操作员离开机台时,放板台、积架、临时PASS台均不能放板,不允许有标识不明的板出现,各放板区全部整理清晰后才可离开机位。同时机台挂上警示牌,其他人员勿动。

C. 多单元的板测试治具要分几次才能测试完整SET,有漏测现象。多UNIT板积架不能一次测完时,先选取一定数量的板每块只测一部分,此批板PASS后在对应部分板边画一条 “颜色线”,再测剩下未测部分。重复以上步骤,直到此批数量板全部划“颜色线”后,才在要求位置画上E-T PASS线。对单元多分几次测试的板一定建议由熟练员工测试,多单元测试的板要清楚机器的性能的操作员才可以上机;

D. 单只报废板漏测

单只报废板测试PASS,漏做、少做、错做,未做报废标记,就会把该报废UNIT当成好板出货,造成漏出。

预防:单只报废测试PASS后随即做上标记,不能测完一批后再统一做,同时应仔细核对实际报废数与标记数是否相符。

2. 设备参数不当导致漏测

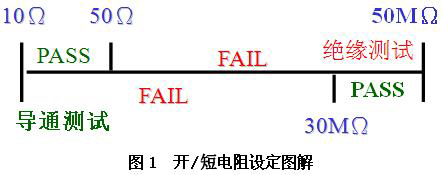

参数一:开路电阻、绝缘电阻

测试参数参见图1:

A.导通测试参数设置越低,代表测试品质越严格,一般的设定范围是10-50Ω;

B.不同表面处理设置不同,一般来说OSP板因为有接触电阻,会设的高些,接近50Ω;

C.绝缘测试参数设置越大,代表测试品质越严格;一般设定的范围是30-50MΩ;

各种测试参数设置及测试精度有所不同,针对传统E-T机架测试进行分析。开路电阻应该在50Ω以内。绝缘电阻应在30MΩ以上。

工厂控制对电测机参数设定密码进行管理,更改参数需要专人修改,其它人员无权限修改。

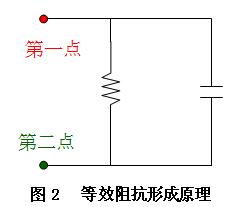

参数二: 治具接触延迟时间

一般来说,我们的待测物PCB,基本上会有电阻与微小电容(多层板间所产生,如图2所示)等特性,而非纯电阻。电容在直流来说,开始充电瞬间视为短路,充完电后视为开路状态。基于这个原理,当测具一接触PAD时,会测到短路,在电容充满电后,才为其真实的状态,而这个充电时间的长短,会依测试电压、电阻档位与线路电容值而变化。所以,在有电容特性的PCB上,若延迟太短,测试结果可能会判为短路,对于短路与绝缘测试来说是误判,同时对于开路测试来说就是漏测了。

一般情况下,为节约时间,我们会设置治具接触延迟时间为0,即治具一接触就开始测试,但相对来说,设定治具接触延迟时间,能减少误测。

3. 测试架本身因素

测试架制作存在漏种针,漏网络的情况,这种情况相对来说较少出现,本文不再详述。

对策:机架制作人员在写资料完成后一定要认真对照治具原始测试点数,完全OK后方可给测试员工测板。任何人不能私自删除资料测试点。

4.PCB板本身因素

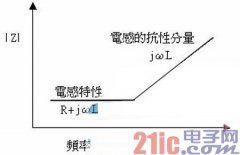

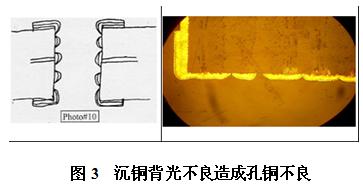

A.沉铜背光不良,孔内铜断断续续。如图3所示:

B. 镀锡不良

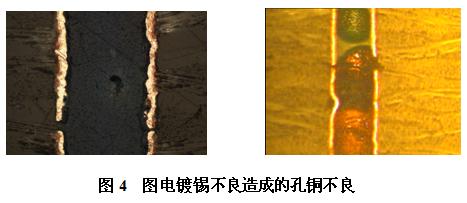

图电镀锡不良(特别是0.5OZ或以下底铜板,因为蚀刻铜厚小于孔壁铜厚容易产生似连非连的情况造成测试误判,包括锡缸气泡和镀锡不良),如图4所示:

C.孔壁铜薄

孔铜全部或局部很薄一层铜,原因包括:

a. 严重氧化,导致二铜很难镀上;

b. 蚀刻过度,返蚀次数过多,锡保护不好;

c. 表面处理的微蚀;

d. 二铜前孔壁有薄薄一层异物,包括干膜碎等;

e. 塞孔不满,残留微蚀药水。

例1:板面电镀前严重氧化

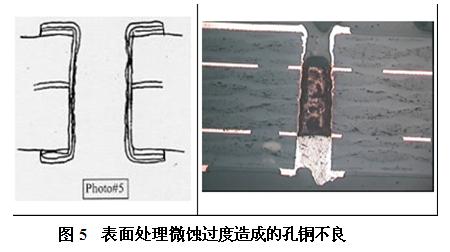

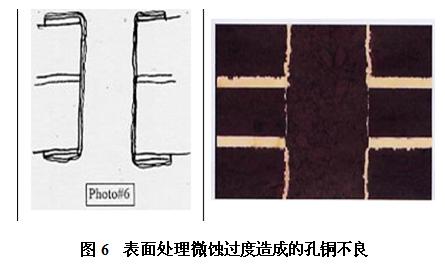

例2:表面处理微蚀过度

以上几类问题都须要在制程中进行管控。对于制程的改善,主要的控制点是沉铜的背光,电镀工序的镀锡不良或者镀锡厚度不够,防焊(绿油)工序的塞孔饱满度管控,表面处理的微蚀量控制以及返工次数的管控,本文就不做详细阐述。

三、 改善方向和方法

PCB 孔破漏测,漏出到客户端,形成PCBA的损失赔偿,一般都是PCB板的20-30倍赔偿,发生此类问题,不仅是经济上的损失,严重的会失去客户。要避免孔破漏测,问题的关键是要根据厂家自己的产品结构特点来布局重点管控,建议如以下点进行改善:

1.人为因素的控制:例如电测工序规划管理,人员培训,防呆装置设计等;

2.设备和治具的管理: 例如参数的设置,积架的制作管理等;

3.生产制程的改善:

A.沉铜的背光控制, 这点目前几乎所有厂家都很严格执行背光检查。

B.底铜是多少,如果多数是0.5OZ或者以下,而且走的是图电流程,那么镀锡的管控就很重要,当然也要延伸到干膜工序,轻微的孔壁残留也会造成镀锡不良。

C.绿油的塞孔是否饱满,有没有裂缝?如果不饱满,有裂缝,在后面的表面处理会残留药水,特别是含铜的微蚀药水,会造成去到客户端还会缓慢腐蚀。

D.表面处理的微蚀量及返工次数管控,微蚀量过大,以及返工次数过多,会造成孔壁铜被蚀去大部分。

目前传统的电测是测不出孔壁还有残铜的PCB,因为设置的电阻一般都高于10欧姆,而孔壁有残铜未蚀干净的PCB,其电阻都是在1欧姆左右,所以测不出。只有低阻测试机可以测出这类板,比如四端子测试机, 就可以对孔到孔,孔到线测试出其电阻,这种电阻可以精确到毫欧级。通过正常板的电阻和问题板的电阻比较,如果差值超过10%,说明铜厚开始有几个微米的区别,如果差别更大,说明铜厚更薄。目前,四端子测试已经越来越被PCB厂家接受,并配置在蚀刻后对特别板做抽测。因为四端子测试机效率不高,通常要五到十分钟才测一块板,所以还不能作为最终的100%测试机来普及,一般用于做抽测,做层别问题板的工具,但是可以避免所担心的孔破问题板漏出去。

关注方式

①直接搜索中文微信号 正天伟科技 即可添加订阅。

②长按括号内的(sz-ztw),可复制,然后到 微信-通讯录-添加 中搜索、免费订阅。

③点击下面的二维码图,保存后扫一扫关注。

| @正天伟科技 微信号:sz-ztw |

*专注于电路板化学品追求卓越,开创无限!

*精彩每周放送,敬请期待!

查看评论 回复