PCB信号完整性仿真与设计之传输线系列(第2期)---传输线反射

高速数字信号的反射是影响现代数字电路设计的重要因素之一,严重的反射将破坏信号的完整性,并引起过冲现象,从而出现错误的数字逻辑和毁坏器件。本文将介绍信号反射产生的现象和机理,阐述造成反射的因素,并给出一些抑制反射的解决方案。

1 传输线反射的现象

反射就是在传输线上的回波。如果一条传输线电尺寸满足长线时,且没有被合理的端接(终端匹配),那么来自于驱动端的信号脉冲在接收端被反射,从而引发不预期的效应,使信号轮廊失真。

反射是传输线的基本效应,即当信号沿着传输线前行时,碰到阻抗不连续时会发生反射:

① 当信号在传输时碰到比目前阻抗高时,会发生正向反射,使信号边沿的幅度增加,信号边沿出线过冲,定义上看,过冲就是接收信号的第一个峰值或谷值超过设定电压;

② 当信号在传输时碰到比目前阻抗低时,会发生负向反射,使信号边沿幅度减小,信号边沿出线台阶,即欠冲,严重时将可能产生假时钟信号,导致系统误读写操作。

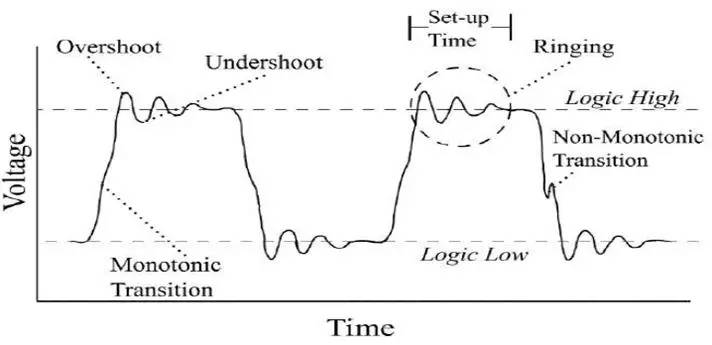

如果在一个时钟周期中,反复出现过冲和欠冲,我们就称之为振荡,也叫振铃。振荡是电路中因为反射而产生的多余能量无法被及时吸收的结果。如下图1所示的波形就是一个明显存在过冲、欠冲而产生振荡的例子。

图1 存在反射现象的信号波形

2 传输线反射的机理

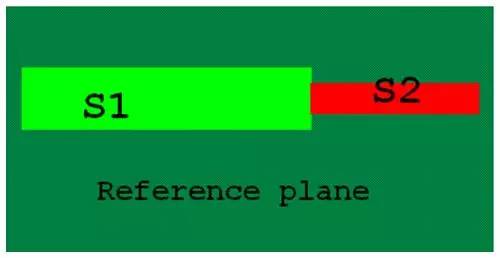

信号在传输线传播过程中,一旦它所感受到的传输线瞬时阻抗发生变化,那么就必将有反射发生。反射是由于传输线瞬时阻抗变化而引起的。下面就从理论角度来分析一下反射的机理,配个简易图2来加以说明。

图2 传输线阻抗不连续简图

图中背景色是电路板上的大面积覆铜层(GND或者PWR),它是信号的返回路径。绿色和红色是传输线,S1比较宽,S2较窄,很明显在S1和S2的交接处出现了阻抗不连续,根据阻抗计算公式应该是Rs1<Rs2。那么信号传输到这里的时候,从反射的定义来看应该是发生了反射。

在交界面,阻抗发生了变化,但电压和电流一定都是连续的,即在交界面的左边一点和右边一点,他们的电压和电流都是相等的。

Rs1=V1/I1

Rs2=V2/I2

V1=V2,I1=I2

其中的V1、V2分别为分界面两侧的电压,I1和I2为分界面两侧的电流。

分析上面的三组方程,如果没有反射,他们是不可能同时成立的。因为Rs1和Rs2不相等,所以可以判定在分界面必定存在反射回源端的信号。

反射系数X定义为反射电压和输入电压的比值,可求得X=(Rs2-Rs1)/(Rs1+Rs2),RS1和RS2分别为传输线阻抗失配分界面前后的瞬时阻抗。

那么这就有3种情况:

① RS1=RS2,即阻抗相等,X=0,即没有反射;

② RS2=无穷大,X=1,即完全正反射;

③ RS2=0,X=-1,即完全负反射,末端接地,阻抗为0,反射信号即可以理解为返回路径上的回流。

反射是经常遇到的SI问题,我们只能无限地缩小它,却不能完全消除它,在波形能够接受的情况下尽量做到最大限度的抑制反射,最重要的就是阻抗匹配。

3 传输线产生反射的因素

产生反射现象的因素有信号上升沿时间、传输线的端接、短分支节线、容性分支节线、拐角和通孔、载重线、电感性间断线等 。在PCB设计中,反射通常由传输线阻抗的不匹配造成,如:不同布线层阻抗不一样、T型连接、拐角和通孔、线宽变化、器件的输入输出阻抗、封装寄生参数。

3.1 传输线串接阻抗不匹配

为了保证信号反射的噪声小于信号摆幅的5%,要求特性阻抗的变化要小于10%,这就是为什么电路板上对阻抗的控制要在+/-10%。

传输线串接阻抗不匹配,如果不连续段的长度很短(不连续段的传输延迟小于信号上升时间的20%),则两端的反射可被约去,不连续就不会产生影响。相反,如果不连续段的长度较长时,信号就会发生反射。根据经验规则,不连续阻抗可接受的最大长度是Len<RT,其中Len为不连续段的最大长度,单位inch;RT为上升时间,单位ns。

3.2 传输线短分支并接阻抗不匹配

传输线短分支并接并不少见,如传输线过孔背钻遗留的尾巴stub就是最常见的传输线短分支并接。

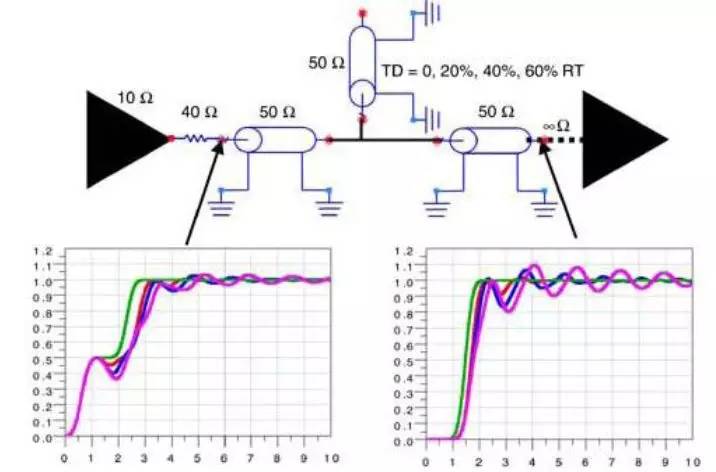

有两个重要因素可决定分支并接对信号完整性的影响,即信号的上升时间和分支的长度。并接分支位于传输线的中间,假设与传输线有相同的阻抗,如下图3展示了分支长度从上升时间的20%增加到60%时,对发射信号和反射信号影响的仿真结果。

图3 传输线并接分支对信号的影响

根据经验规则,分支长度时延保持小于上升时间的20%,则分支的影响就不重要,反之对信号的就会产生影响。可用经验式子来表示:Lstub<RT,其中Lstub为可接受并接分支的最大长度,单位为inch;RT为信号的上升时间,单位为ns。

3.3 传输线拐角的阻抗不匹配

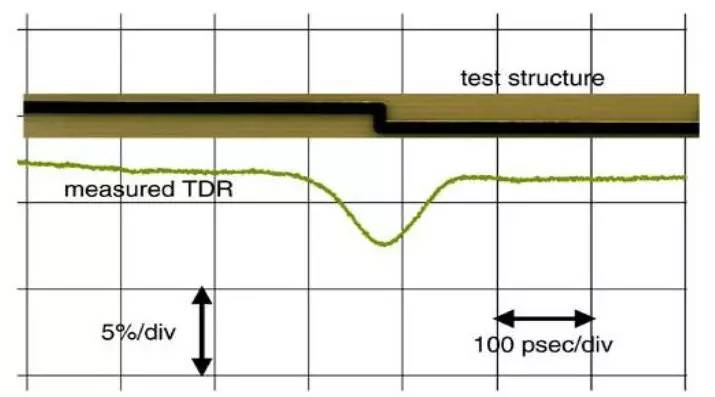

信号沿着均匀的互连线传输时,发射信号不存在反射及失真。如果均匀互连线存在90度的弯曲,就有阻抗的改变,则发生反射及信号的失真。如下图4是对上升时间为50ps的信号所做的TDR响应,附近有2个90度的拐角,阻抗不连续而导致反射。

图4 传输线上存在90度拐角时信号的TDR响应

拐角对信号传输线的唯一影响是由于走线弯曲处的额外宽度,这个额外的线宽作用就像一个容性的不连续性,导致了信号的反射和时延。将90度的拐角转换为45度的弯曲将会减小这种影响,如果改用长宽的圆弧状弯曲,影响会进一步减小。

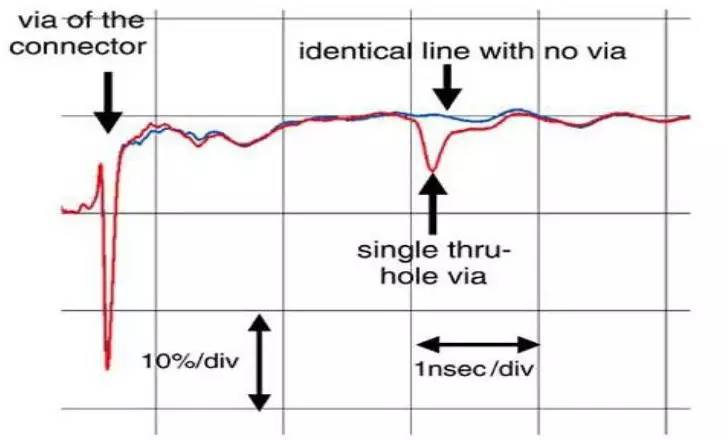

3.4传输线通孔的阻抗不匹配

PCB上经常需要通孔来连接两根信号线,实现不同层的信号传输。通孔对于PCB的不同层具有过多的电容,这时,通孔可看作是一个集总的电容负载,其电容的大小依赖于孔的大小等物理结构。

信号线上任一通孔都可以看作是容性的不连续性,在高速互连中,是影响信号完整性的重要因素。如下图5所示的是在10层板中,10inch长的均匀走线上带有通孔和不带通孔时测量的TDR响应,可见通孔造成了传输线阻抗的不连续。

图5 传输线上存在通孔时信号的TDR响应

4 抑制传输线反射的端接技术

消除传输线反射现象的方法一般有:布线是的拓扑法和相应的端接技术。

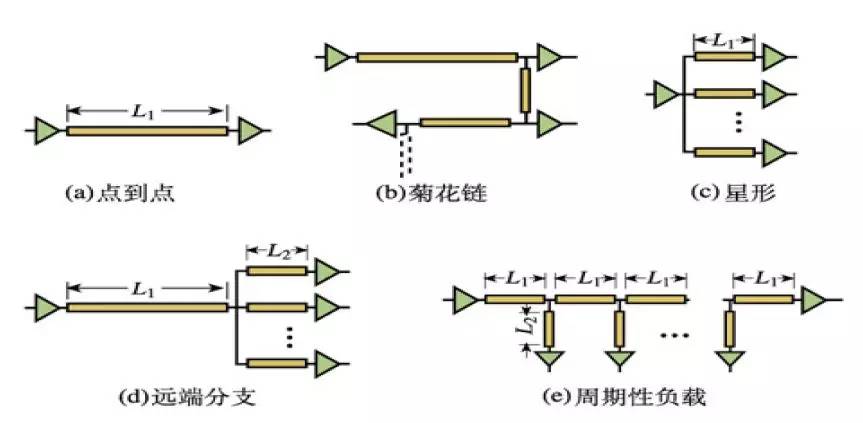

常用的布线时的拓扑结构有:点到点、菊花链、星形、分支和周期性负载等,如下图6。

图6 常见的几种端接结构

(a)点到点:这种拓扑结构比较简单,只要在发送端和接收端进行适当的阻抗匹配;

(b)菊花链:当网络的整个走线长度延迟小于信号的上升或下降时间时,用菊花链拓扑结构比较好,这时网络上的负载都可以看做容性负载,菊花链同时限制了信号的上升速率,也只能工作在低速电路中;

(c)星形:使用星形拓扑结构时,对每个分支stub都要进行均衡设计,要求分支的接收负载一致,并选择适当的匹配方式;

(d)远端分支:与星形结构类似,只不过分支是靠近接收端;

(e)周期性负载:要求每段stub的长度足够小,使stub上的传输延时小于信号上升沿。

传输线上的反射会对数字系统性能有重要的负面影响,为了最小化反射的负面影响,除了从拓扑结构上消除影响外,还必须有相应控制他们的方法。通常的方法是给传输线两端接一个等于特性阻抗的阻抗,并消除反射,即所谓的高速电路设计端接技术。

当然,上述方法并不是绝对的,具体电路有差别、传输线的走线方式也不一样,在设计时需要根据具体的情况通过仿真来选取最佳的抑制传输线反射的方案。

查看评论 回复

"PCB信号完整性仿真与设计之传输线系列(第2期)---传输线反射"的相关文章

- 上一篇:铜价扬升 金居4月铜箔涨1%

- 下一篇:详解PCB电路板多种不同工艺流程