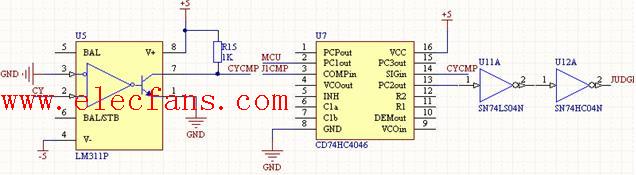

����ȽϺ���λ�Ƚϵ�·ԭ��ͼ - ��ģ��� -

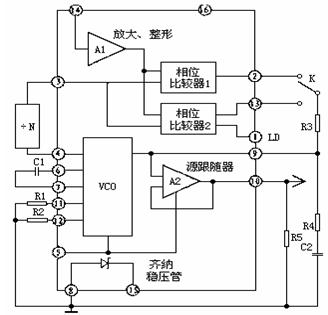

����Ƚ��������λ�Ƚ�����·ԭ��ͼ��ͼ

���ڳ�ʹ�ü��ɵ�·�����CD4046����ͨ�õ�CMOS������ɵ�·�����ص��ǵ�Դ��ѹ��Χ����Ϊ3V��18V���������迹��(Լ

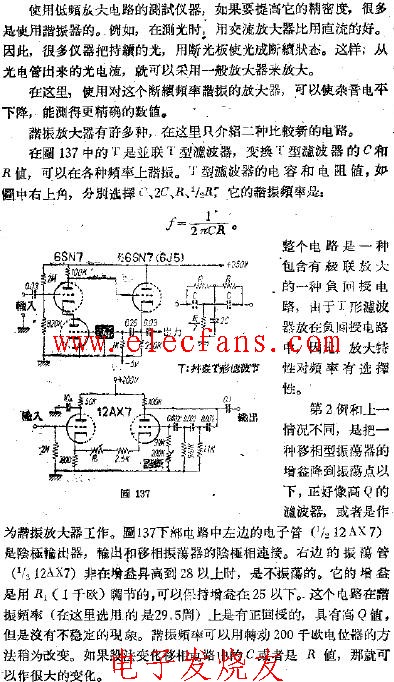

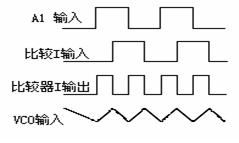

1����λ����ˣ���·����ʱΪ�ߵ�ƽ����·ʧ��ʱΪ�͵�ƽ��2����λ�Ƚ����������ˡ�3�űȽ��ź�����ˡ�13����λ�Ƚ����������ˡ�14���ź�����ˡ�����λ�Ƚ�������ԣ���14�ŵ������źű�3�ŵıȽ��ź�Ƶ�ʵ�ʱ�����Ϊ����

ͼ2.13 �Ƚ����������ͼ

�������������������������� �鿴���� �ظ�

"����ȽϺ���λ�Ƚϵ�·ԭ��ͼ - ��ģ��� -"���������

- ��һƪ������ת����·ԭ��ͼ - ��ģ��� -

- ��һƪ����������·ͼ - ��ģ��� -

��������

- ģ�⼯�ɵ�·�IJ��Լ���-ģ�����-

- ��γ�Ϊ��ɫ��ģ���ʦ:���ָ�����ģ�����-ģ���

- ���ģ�������MEMS��˷��������-ģ�����-

- �����¶ȼƵ�ģ�ⲿ�ֵ�·ͼ-ģ�����-

- �����ⲿ�ж�ʵ��ģ������ݵ��շ�-ģ�����-

- ������/�����̻���ɡ�ģ��뵼��ӭ��ɳ�������-ģ��

- TI�߾���ʵ�������߿γ� �����ɫ����ģ����ƴ���-ģ

- ģ��ʾ����������ʾ����������-ģ�����-

- ������PLC���ڷ�ģ�����������-ģ�����-

- �û���ź�ʾ����̽��ģ��������ź�-ģ�����-