逐次逼近A-D转换器充分利用数字校正及冗余性-模拟电子-

在“ISSCC 2010”的Session21“Successive-Approximation ADCs”上,仅逐次逼近A-D转换器一项就占满了整个会程,足见其性能得到长足进步。无需放大器的逐次逼近是一种适于微细化及低电压化的架构,有很多发表都与充分利用数字校正及冗余性来发挥该架构的特点有关。

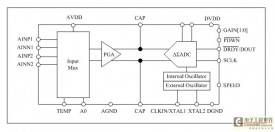

发布的内容大致分为三类。第一是利用逐次逼近力争实现高精度。具体而言,模拟器件发表了面向医用X射线数字图像处理的18bit、12.5MHz的 A-D转换器(演讲序号为21.1)。通过对2bit逐次逼近进行两级管线化,实现了18bit、12.5MHz的性能。不过,电源电压为 5V/2.5V,并同时使用0.5μm/0.25μm元器件。高位10bit使用4个逐次逼近阵列每2bit进行确定,低位bit也由瞬时A-D转换器每 2bit进行确定。利用42倍放大器对高位和低位进行耦合,通过管线工作提高速度,使用1bit冗余转换来放宽放大器的要求精度。而容量失配则通过数字校正进行修正。

第二是通过实际验证证明,能够以1.0V~1.2V的低电压,以及820uW~3mW的低功耗,实现以往管线所擅长的8~12bit、10~100M采样/秒(演讲序号为21.2~21.6)。该技术以通信及医用信号处理所需要的低功耗A-D转换器为对象。

伊利诺大学香槟分校通过将通常以二进位使加权增至2倍的容量阵列增至1.85倍,通过校正消除了容量失配(演讲序号为21.2)。由于消除了失配的制肘,因此可将容量阵列减至由kT/C噪声决定的最小值。22.5M采样/秒模式使用底噪校正实现了11bit的精度。

东芝通过用90nm工艺在高位逐次逼近和低位逐次逼近之间插入放大器,减小了整体的面积功率(演讲序号为21.3)。在40M采样/秒、1.2mW下以0.06mm2实现了8.9bit有效bit。

富士通研究所利用称为分割阵列的方法来分割容量阵列,通过补偿D-A转换器对发生的误差进行了修正(演讲序号为21.4)。使用数字校正在50M采样/秒及820μW下得到了9.0bit有效bit。使用65nm工艺制造技术,面积减少至0.039mm2。

台湾成功大学(National Cheng-Kung University)等通过在级间插入冗余转换阶梯来修正因容量D-A转换的设定时间不足而发生的转换误差,由此提高了速度(演进序号为21.5)。在 100M采样/秒下成功得到9.5bit有效bit,而且功率也降至1.13mW,在Figure of Merit (FoM)上获得15.5fJ/conv.-step的最高值。Holst Centre-IMEC尽管得到的分辨率仅为8bit,但将容量阵列的单位容量降到了1fF,而且10M采样/秒时功率也非常低,只有69uW(演讲序号为21.6)。

第三是实现了超高速的A-D转换器。北电网络进一步改进了在“ISSCC 2008”上发表的技术,通过交错16个6bit逐次逼近A-D转换器,实现了全球最快的40G采样/秒的速度(演讲序号为21.7)。

这些发表令人预感到,随着今后微细化及低电压化的发展,逐次逼近将成为主流架构。(特约撰稿人:松浦 达治,瑞萨科技)

查看评论 回复