Xilinx fir滤波器IP

来源:网络整理 网络用户发布,如有版权联系网管删除 2018-07-02

1、 系数由matlab中的fdatool产生,放入coe文件中,

radix=10;

coefdata=

-1 , …………-1;

2、可以选择滤波器的类型,此处选择插值滤波器,插值倍数设为8.

3、时钟: input sampling frequency 输入该滤波器数据的采样速率。

clock frequency fir IP核的工作时钟,

他们之间的关系为 clock frequency > input sampling frequency * N (N 插值倍数)

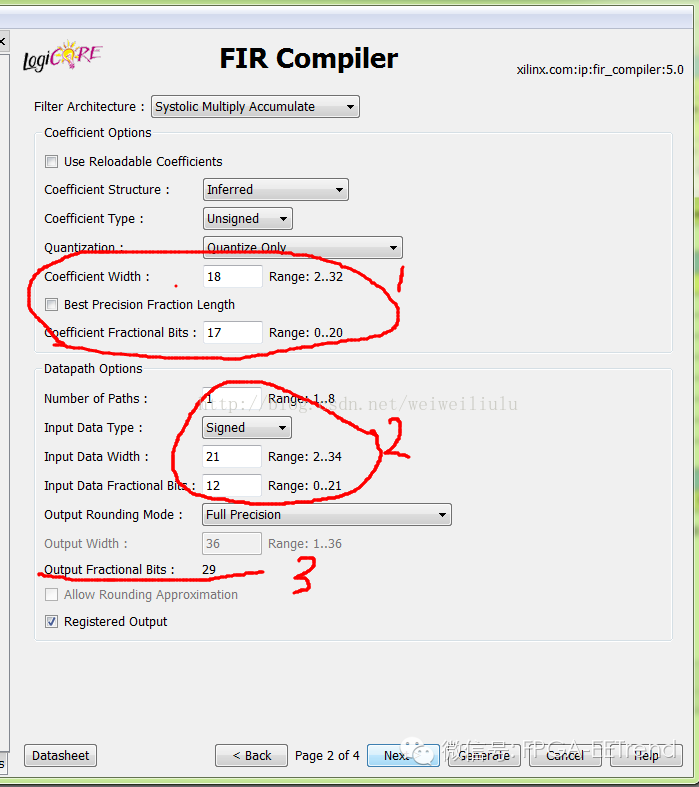

1、 输入系数位宽和小数点位数

输入系数位宽是系数文件导入后自动生成的,系数小数点位宽可以自动生成,也可以自己设定。比如在系数文件中,第一个数据为-1 。但是在FPGA中, 没有小数的概念,所以coefficient fractional 系数小数位也就是将系数左移了17位

2、输入数据位宽。原始数据的位宽是9比特,但是为了提高精度,将数据左移 12位(input data fractional bits)。assign data_fir = {data_source , 12'd0};在matlab中,左移12位,就是乘以2^12. xilinx中,输入数据小数位是多少,就需要将原始输入数据左移多少位。

3、输出数据位宽。输出数据小数位位宽为29 = 12+17. 如果要将matlab中的数据和xilinx中的数据对比,就需要将matlab中的数据左移17位。有的时候需要将输出数据位宽截取N位,,则matlab中左移位数为17 -N。

文章转载自: http://blog.csdn.net/weiweiliulu/article/details/40151053

查看评论 回复