从Multicore到Many-Core:体系结构和经验 - IP核设计 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-11

您可能已经习惯了芯片系统(SoC)的mulTIcore处理器这一概念,而现实却总是在不断变化。8月份举行的Hot Chips大会研讨中,已经清楚的表明mulTIcore正在向many-core发展:在SoC核心位置,密切相关的处理器内核的数量在不断增长,从2个或者4个增加到8个、16个,甚至是很多,很多。

这种增长仅是摩尔定律发展的另一阶段,系统开发人员还是能清楚的了解这一切吗?从mulTIcore发展到many-core是类型的变化,还是仅仅是规模的变化?这种转变能解决系统开发人员面临的问题吗?

为找到这些问题的答案,我们与一些团队进行了交流,他们已经在many-coreSoC开发上积累了一些设计经验。我们向他们提出了一个简单的问题:您的体验与使用mulTIcore有什么不同吗?对于这一简单的问题,我们得到了各种各样的回答。

Many-core的发展

Hot Chips的论文列出了SoC体系结构向many-core领域发展的三条主要路线。我们从Cavium的Kin-Yip Liu在小规模无线基站SoC设计论文中阐述的路线开始,这些设计包括微基站、微微基站和毫微微基站。

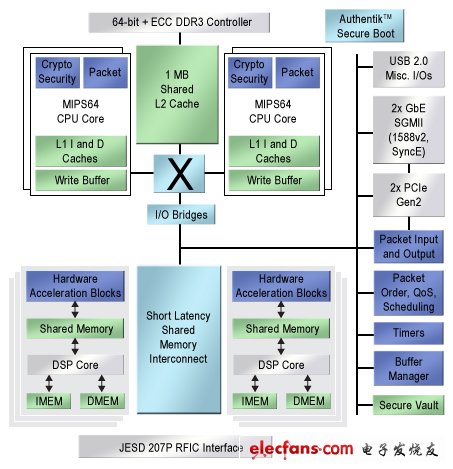

名为Octeon Fusion CNF71xx的设计如 图1 所示,包括两个处理簇,含有四个一组的增强MIPS64内核,以及围绕一个共享L2高速缓存的各种硬件加速器,还有6个为一组的数字信号处理(DSP)内核,每个内核都有很多硬件加速器,这些内核分布在共享存储器交换架构周围。

图1.Cavium的Octeon Fusion体系结构结合了CPU簇以及相连接的硬件加速器和分立的DSP内核簇。

查看评论 回复