基于CPLD/FPGA的CMI编码设计与实现 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-15

0 引言

CMI码是传号反转码的简称,它是一种应用于PCM四次群和光纤传输系统中的常用线路码型,具有码变换设备简单、有较多的电平跃变,含有丰富的定时信息,便于时钟提取,有一定的纠错能力等优点。

在高次脉冲编码调制终端设备中广泛应用作接口码型,在速率低于8 448 Kb/s的光纤数字传输系统中也被建议作为线路传输码型。

本文针对光纤通信传输码型的要求和CMI码的编码原理,介绍了一种以EPM系列7064芯片为硬件平台,以Max+PlusⅡ为软件平台,以VHDL为开发工具,适合于CPLD实现的CMI编码器的设计方案。

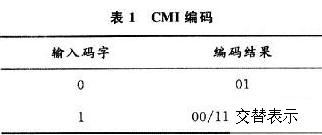

1 CMI码的编码规则

CMI编码规则如表1所示。