AES中的字节替换的FPGA实现 - FPGA/ASIC技术 -

介绍AES中的字节替换算法原理并阐述基于FPGA的设计和实现。为了提高系统工作速度,在设计中应用了流水线技术。最后利用MAXPLUS-II开发工具给出仿真结果,并分析了系统工作速度。

1 引言

目前,加密算法按照加密特点分为对称密文和不对密文二大类。AES [1](Advanced EncrypTIon Standard)是NIST(NaTIonal InsTItute of Suandard and T echnologies)继2000年10月选择Rijndael算法[2]之后,于2001年11月26日发布的新的对称数据加密算法。

本文首先介绍AES中的SubBytes(字节替换)概貌,并解析出它使用的算法原理,然后论述基于FPGA技术对AES中的字节替换仿真的设计与实现。笔者在运用FPGA技术的过程中完全采用NIST公司的AES算法标准。为了获得在面积和速度上的最佳优化,将流水线设计技术应用到本设计中。另外,本文所得到的仿真结果是在MAXPLUS-II 10.0上运用Verilog HDL硬件描述语言来实现的。

2 AES中的Subbytes算法描述

AES算法的核心有4种操作[3]:SubTytes(字节替换)、ShiftRows(行位移变换)、MixColumns(列混合变换)和AddRoundKey。这里,主要对SunBytes(字节替换)算法进行描述。

2.1 SunBytes字节替换

字节替换重要的是将一个8位数据转换为另一个不同的8位数据,这里要求一一对应,并且替换结果不能超出8位。例如将00H转换成63H。这个重要的特性正好符合Galois Field(GF)-伽罗瓦域特性。由于转换的数据是8位的,所以符合GF(28)域特性,即GF(28)域中进行的加法或乘法操作的结果必须在{0x00 ...0xff}这组数中。虽然GF()域论是相当深奥的,但GF()域加法的最终结果却很简单,GF()加法就是异或(XOR)操作。关于GF()加法和乘法,将在2.3字节中进行描述。

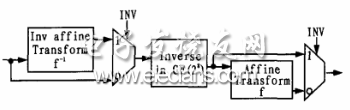

根据NIST描述的ASE算法标准,SunBytes字节替换连续进行以下变换便可达到替换要求。

(1)在GF(28)域中进行乘法变换,即实现多项式m(x)=x8+x4+x3+x+1变换,称之为“mulTIplicative inverse”。

(2)在GF(28)域中进行交换来实现如下矩阵,称之为“affine transformation”。例如“CA”被变换成“ED”。