基于FPGA和VHDL的数字密码锁的设计与实现 - 参考设计 -

自古以来人们对物品安全就十分重视,数字化的今天,电子锁正在逐步取代以往的机械锁被广泛运用在门禁、银行和保险柜。然而,这些基于单片机的密码锁可靠性较差,而且功能拓展有限。随着物联网技术的发展,人们对电子锁安全性和可靠性又提出了新的要求。本文所述的FPGA,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。由于其高集成度,使得电子产品在体积上大大缩减,且具有可靠、灵活、高效等特性,己备受设计师们的青睐。

1 系统概述

1.1 功能概述

(1)初始密码为000000,按C键设置密码,密码设置完成后按A键即上锁。

(2)以4&TImes;4键盘为输入设备,按B键开始密码输入,串行输入6位密码,输入完成后按#键,确认密码输入完成。七段数码管将显示用户所输入的数字。

(3)密码输入正确,则开锁指示灯灭,若密码输入错误或位数不足,报警灯亮。

(4)处于报警状态时,按*键可解除报警。

(5)为保证安全,系统只有在开锁状态时,按C键,用户才可重新设置密码。

1.2 系统结构

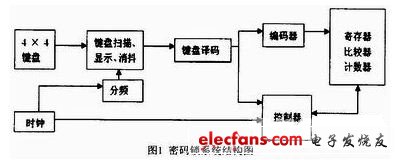

系统以4&TImes;4矩阵键盘为输入设备,七段数码管和指示灯为系统的输入显示和输出指示器。系统内部可分为以下几个模块:键盘扫描及消抖电路、分频电路、译码电路、编码器、寄存器、比较器、控制器、计数器。系统结构大致如图1所示。

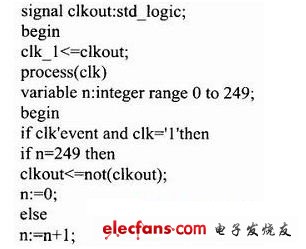

按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合或断开时不会稳定地接通或立即断开,在电路上则会表现为连续地输入同一个值。因此在键盘扫描电路里加入了键盘消抖程序。为使用户能够看到自己所输入的密码,将七段数码管的显示电路也集中到了键盘扫描电路内。键盘扫描所用的时钟频率为1kHz,故将系统所用的1MHz的时钟分频为1kHz供键盘扫描用,以分频模块为例,其程序如下:

查看评论 回复