基于Altera CPLD的水轮发电机组转速监控系统的设计 - 参考设计 -

电子发烧友网核心提示:本文给出了采用CPLD的水轮发电机组转速监控系统的设计原理和VHDL的语言描述,该设计具有结构简单、成本低和抗干扰性能强等特点。

1 概述

转速数据是水轮发电机组运行状况的重要标志之一。准确地测量机组的转速并根据转速的变化及时地进行各种必要的控制操作,以保证水轮发电机组正常、安全运行,是该监控装置应完成的功能。目前,国内水电站使用的大多是永磁发电机加电压继电器式、机械式等旧式转速信号器,存在结构复杂、测量精度低、工作可靠性差等缺点。本文所述的水轮发电机组转速监控系统是采用 CPLD(ComplexProgrammable Logic Device)及少量的接口器件构成的,系统的功能结构描述采用VHDL(Very HighSpeed Integrated Circuit Hardware DescripTIonLanguage)。由于采用的CPLD芯片能够高密度、高速度、高性能地实现复杂数字系统的设计,使硬件设计大大简化。具有设计硬件结构简单、测量精度高、抗干扰能力强等特点。

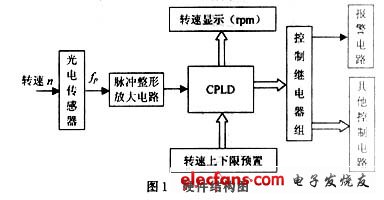

2 设计原理硬件结构

如图1所示。CPLD芯片是整个系统设计的核心器件。

2.1 转速传感器

本设计中的转速传感器采用光电式脉冲编码器,与待测发电机主轴同轴相连。传感器上均匀分布有60个感光孔,使转速为n的水轮发电机,每分钟有60n个脉冲输出,即每秒有n个脉冲,故可以通过对传感器的输出脉冲频率fp的测量得到水轮发电机的转速值n(脉冲频率fp与转速n在数值上相等)。

2.2 输入电路

输入电路由施密特触发器和光电耦合器件构成,对光电传感器的输出脉冲信号进行整形放大,并实现光电传感器与CPLD的输入隔离,提高系统的工作可靠性。

查看评论 回复