基于FPGA技术的数字相关器的设计与 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

【摘 要】 用VHDL设计了一种32-bit数字相关器,测试和实际应用表明其性能稳定可靠。

关键词:FPGA,VHDL,相关器

1 引 言

同步在通信系统中占有非常重要的地位,同步系统性能的高低在很大程度上决定了通信系统的质量,甚至通信的成败。相关器是同步系统的关键部件之一,因此,要求相关器须有比其它部件更高的可靠性。实际应用中,相关器可用软件实现也可用硬件电路实现,后者更适合于高速数据通信中的相关检测。本文在总结一般数字相关器设计的基础上,设计实现了一种高性能的数字相关器。

2 数字相关器的一般原理

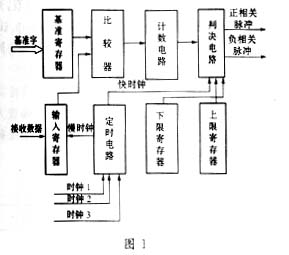

数字相关器的一般原理如图1所示。