可编程ASIC器件主从式结构开发系统 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

1 引言

当前在EDA领域,只要具备台式或笔记本电脑并装有工具软件,就可以方便地对可编程ASIC(CPLD/FPGA)进行设计开发,在系统可编程(ISP)器件为我们提供了这种便利条件。ISP方式虽然可以用一根下载电缆代替了编程器,但兼有提供下载和演示环境两大功能的可编程ASIC开发系统对于用户来说仍是必须的。本文提出的主从式下载开发系统可以适配多种目标芯片,具有较宽的开发应用范围,经过几年的教学、科研实践,使用效果良好。

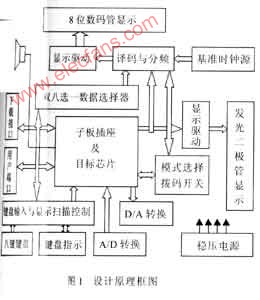

对ASIC器件设计开发的前期工作主要依靠对某种EDA工具软件使用。对于其工具软件和硬件编程语言,必须通过实践锻炼方能熟练使用和达到掌握技巧的程度。对应用系统和目标芯片进行开发,先要使用EDA工具软件所提供的文本和图形输入方式进行描述和综合,并要通过仿真验证。而后的工作就是将设计完成并通过仿真的熔丝图文件对目标芯片下载,并在系统板提供的开发环境中直接进行功能演示。因而下载开发系统的基本结构必须具备输入和输出功能。设计数字电路或系统往往需要多种频率资源,故系统板要提供时钟配置和频率选择功能。而要完成开发系统的复杂工作和模式选择,系统控制功能也是必须的。基于以上思路设计开发的系统电路框图如图1所示。

"可编程ASIC器件主从式结构开发系统 - FPGA/ASIC技术 -"的相关文章热门文章

相关文章

热门文章论坛热帖网站地图 |