FPGA实现原型板原理图的验证 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

首次流片成功取决于整个系统硬件和相关软件的验证,有些公司提供的快速原型生成平台具有许多调试功能,但这些平台的价格非常高。

因此最流行的做法是根据DUT和具体应用设计复合FPGA板,验证这些板的原理图通常是很麻烦的,本文提出一种利用FPGA实现原型板原理图验证的新方法。

由于价格竞争越来越激烈,首次流片成功或只需少量的修改变得越来越重要。

为了达到这一目标,对整个系统(即硬件和相关软件)的验证成为重中之重。

业界也涌现了许多策略来帮助设计师完成RTL上的软件运行。这些策略提供了在最终硬件还在酝酿之时就开发软件的一种途径。

这种措施也许还不够,原因还有两个:一是仿真系统可能与实际系统有较大的区别,二是系统运行速度非常慢。因此可以考虑先将完整的设计映射到FPGA中,再运行目标应用程序。

这样做可能达不到最终硅片的常规指标,但可以测试整个硬件的功能,系统能够得到全面的验证,其中一些测试案例可能是在仿真中根本无法完成的。另外,可用于演示的完整系统原型在硅片成功之前就可以很好地引起客户的兴趣。

有些公司提供的快速原型生成平台具有许多调试功能。这些电路板平台具有可编程的互连,可以将FPGA插接在上面,并将DUT(被测设计)映射进这些FPGA中。但这些平台的价格非常高。

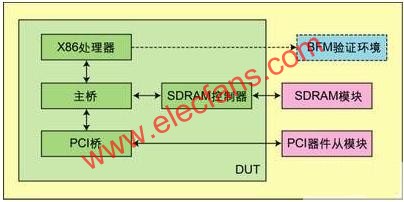

因此最流行的做法还是根据DUT和具体应用设计复合FPGA板。当然,这些板同样也能用于测试目标应用中的最终硅片。

验证这些板的原理图通常是很麻烦的,因为原理图中一些小错误会严重影响到设计进度。

原理图验证工作是人工完成的,因此错误也就在所难免。如果能够复用DUT验证环境验证电路板原理图,那么原理图验证就可以派上用场了。本文将讨论如何通过编写少量脚本和修改DUT验证环境达到这一目的。