FPGA在高速互连中的应用 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

高速串行互连是标志并行数据总线向串行总线转变的技术里程碑,这种技术是减少设计师面临的信号阻塞问题的方法。这种转变是由业界对系统成本和系统扩展能力的要求所推动的。随着芯片技术的发展和芯片尺寸的缩小,用速率达数千兆位的高速串行互连来取代传统的并行结构变得简单易行。

技术发展

低压差分信号技术(LVDS) 是隐含在许多高速串行互联标准定义后面的核心电子信号技术。当数据率高于3Gbps时,电流模式逻辑 (CML) 和低压正射极耦合逻辑(LVPECL) 是关键技术。

功耗和数据率是取舍各种信号技术方法的关键因素。

为进一步降低信令引脚的数量和信号布线的长度,从而降低电路板的设计复杂程度,时钟被嵌入到了数据中。在接收端,需要对时钟数据进行恢复,这种方法已经发展成熟并被许多串行通信系统所广泛采用。

此外,为提高抗噪能力和共模抑制能力,LVDS信号技术大多采用交流耦合。这就需要直流平衡线路编码方案并保持有足够的切换用于时钟恢复。我们采用IBM开发的8b/10b编码方案或类似的方案,将8位字转化成10位的符号并最终用于传输。8b/10b编码还包括用于同步的特殊控制字符(被称为“K字符”) 。

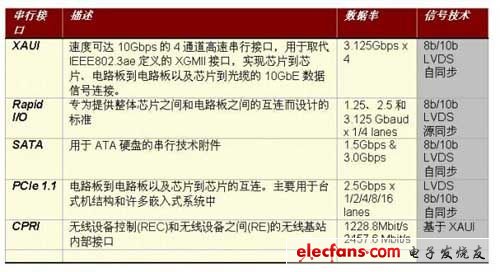

高速串行接口通常用于各种芯片之间的接口、背板的互连以及设备与设备的连接。以下是被广泛采用的一些串行互连协议:

芯片到芯片/背板串行互连:

XAUI

Rapid I/O

SATA

PCIe

CPRI (控制设计和基站间的3G通信协议)

硬件机箱设备与设备的串行电缆接口:

HDMI, DVI, 显示端口

USB

1394