利用FPGA实现与DS18B20的通信功能 - FPGA/ASIC技术 -

1、概述

本文介绍利用ACTEL公司的ProASICplus系列FPGA实现与DS18B20的通信功能。FPGA可以将读出DS18B20的48位ID号和12位温度测量结果保存在内部寄存器中,微处理器可以随时快速地从FPGA寄存器中读取这些信息。

一般在使用DS18B20时往往采用微处理器的I/O端口实现与该器件的通信,这种方法虽然比较容易和方便,但是,因为DS18B20的一线式串行总线对时序要求比较严格,因此,为了保证与DS18B20的通信可靠性,微处理器与DS18B20通信时需要采用关闭中断的办法,以防止操作时序被中断服务破坏。

利用FPGA实现与DS18B20通信不存在被迫关闭中断的情况,可以满足对实时性要求严格的应用要求。

2 ProASICplus系列FPGA简介

ProASICplus系列FPGA是ACTEL公司推出的基于Flash开关编程技术的现场可编程门阵列,包括从7.5万门的APA075型到100万门的APAl000型,具有高密度、低功耗、非易失、含有嵌入式RAM及可重复编程等特点。

因为ProASICplus系列FPGA基于Flash技术,利用Flash开关保存内部逻辑,因此不需要另外的器件。由于不需要上电配置过程,因此具备上电就立即工作的特点。不用配置器件,系统的保密性提高。

笔者在电力监控的产品中利用APA150型FPGA实现了逻辑控制、A/D采样控制和FIFO存储等功能,并利用剩余的资源实现了DS18B20的通信功能。APA150在整个系统中充当协处理器,使主CPU从繁重的实时处理中解脱出来。

3 DS18B20简介

3.1内部结构

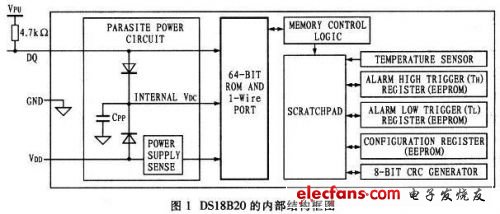

DS18B20的内部结构如图1所示,主要由以下几部分组成:64位ROM、温度传感器、非挥发的温度报警触发器TH(温度高)和TL(温度低)、配置寄存器、暂存寄存器(SCRATCHPAD)、存储器控制逻辑。DQ为数字信号输入/输出端。

ROM中的64(8位产品家族编号、48位ID号、8位CRC)位序列号是出厂前刻好的,这64位序列号具有惟一性,每个DS18B20的64位序列号均不相同。

8位CRC生成器可以完成通信时的校验。

暂存寄存器有9个字节,包含温度测量结果、温度报警寄存器、CRC校验码等内容。

3.2操作步骤

对DS18B20的操作分为3个步骤:初始化、ROM命令和DS18B20功能命令。

3.2.1初始化

FPGA要与DS18B20通信,首先必须完成初始化。FPGA产生复位信号,DS18B20返回响应脉冲。

3.2.2ROM命令

该步骤完成FPGA与总线上的某一具体DS18B20建立联系。ROM命令有搜寻ROM(SEARCH ROM)、读ROM(READ ROM)、匹配ROM(MATCH ROM)、忽略ROM(SKIP ROM)、报警查找等命令(ALARM SEARCH)。

这里,FPGA只连接1个DS18B20,因此只使用读ROM命令,来读取DS18B20的48位ID号。