基于FPGA的卷积码译码器的方案 - FPGA/ASIC技术 -

卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。它克服了分组码由于以码块为单位编译码而使分组间的相关信息丢失的缺点。(2,1,8)卷积码在2G、3G通信系统中得到了广泛的运用。CDMA/IS-95系统的前向信道[3]、CDMA20001x的前反向链路都使用了生成多项式为(561,753)码率为1/2的(2,1,8)卷积码。针对目前卷积码译码器占用资源较多,最高工作频率较低的缺点,本文设计了一种新的基于FPGA的(2,1,8)卷积码译码器。该译码器工作频率高,输出时延小,占用资源少。

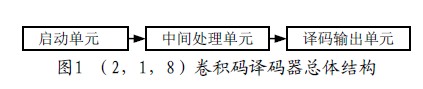

1 (2,1,8)卷积码译码器的总体设计

本文所实现的(2,1,8)卷积码译码器是基于维特比算法的硬判决译码器。整个系统分为启动单元、中间处理单元、译码输出单元3个单元模块。系统总体结构图如图1所示。对(2,1,8)卷积码译码器,启动单元处理的是前8个输入的码字,中间处理单元处理的是后续输入的码字。译码输出单元实现对译码器译出码字的输出。本设计中,各状态节点的路径度量和幸存路径均采用FPGA片内的寄存器作为存储主体,即采用的是寄存器交换法。这样译码输出时不用回溯,能极大提高译码器的译码速率。

2 (2,1,8)卷积码译码器各模块设计

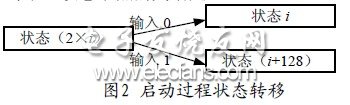

2.1 启动单元模块

(2,1,8)卷积码译码器共有256个状态节点。在处理前8个输入码字中的第i(i为大于0且小于9的整数)个码字时,只需对其中的2i个状态节点进行处理,而且转移至这2i个状态节点的前一状态节点都各仅有一个,其状态转移图如图2所示。因此并不需执行比较和选择操作。该单元的关键在于确定处理第i个码元时,需对哪些状态节点的幸存路径和路径度量值更新。经分析可知:在第i个码元处理结束后。当且仅当某节点对应的状态值的二进制形式的低(8-k)位比特均为0,译码器才可能到达该状态节点。据此本文设计了如下的一种巧妙方法确定某状态节点是否能到达。设置一个8bit位宽的寄存器型变量sd0。其初始值置为0x7f,即将其最高位置为0,每处理完一个码元,就将sd0右移一位,在判断状态值为i的节点是否需要处理时,将sd0与i进行按位与运算,若其结果为0,则该状态节点需被处理,否则,直接进入对下一状态节点的判断处理。

在计算各状态节点的路径度量BM时,本设计采取了如下方案。预先计算出(2,1,8)卷积码的256个状态在输入为0时的编码结果,并将其存储在一个由256个位宽为2bit的寄存器组中。处理接收的卷积码码字时,首先计算出该码字与(2,1,8)卷积码的4个可能码字00,01,10,11的不同的比特的位数。并分别存储在对应的4个2bit位宽的路径度量寄存器l0,l1,l2,l3中。将状态节点i和(i+128)的两个路径度量值分别记为BM0和BM1,节点i的BM0和BM1分别为编码器处于状态(2&TImes;i)和(2&TImes;i+1)且输入为0时的输出码字与当前时刻输入码字不同的比特数。节点(i+128)的BM0和BM1分别为编码器处于状态(2&TImes;i)和(2&TImes;i+1)且输入为1时的输出码字与当前时刻输入码字不同的比特数。且任何状态节点的两个路径度量值BM0和BM1之和为2,据此就可得出各个状态节点的BM0和BM1的值。

2.2 中间处理单元

中间处理单元的主体是加比选操作模块。(2,1,8)卷积码译码器处理完开始的8个码元之后,其状态转移图如图3所示。此时,到达每个状态节点的路径有两条,到达状态节点i和i+128的两条路径分别来自节点2×i和2×i+1,其中i为小于128的自然数。对状态i和i+128对应节点的幸存路径和路径度量值的更新就是要比较节点2×i和2×i+1的在前一码元处理结束后的路径度量与它们转移至状态i和i+128时对应的路径度量之和,并取其中较小者。

该单元需解决的一个关键问题就是路径度量的溢出问题。若不对该问题进行处理,随着译码序列长度的增加,将根据各状态的路径度量寄存器存储值的大小判断各状态路径度量的相对大小发生错误,从而使得译码出错。经过对(2,1,8)卷积码译码器网格图的研究发现:硬判决时,256个状态的路径度量的最大值与最小值之差不会超过15,若用5比特位宽的寄存器型变量存储各状态的路径度量,当最大路径度量值达到31即将溢出时,最小路径度量值一定不小于16,此时将所有256个状态节点的路径度量值均减去16,这样就解决了溢出问题。根据各状态的路径度量值的最高比特位是0还是1就可判断其值是否大于等于16。

查看评论 回复