LatticeECP4高速可配置SERDES - FPGA/ASIC技术 -

电子发烧友网:本文主要讲述的是LatticeECP4高速可配置SERDES。

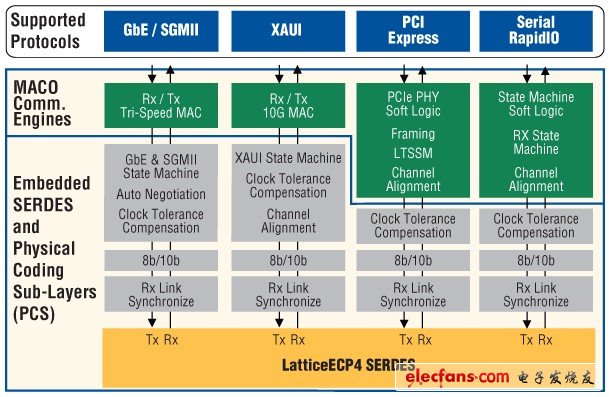

LatTIceECP4™ FPGA系列结合了高性能FPGA结构、高性能I/O和多达16个通道的嵌入式SERDES,带有相关的物理编码子层(PCS)逻辑。每个PCS逻辑通道包含专用的发送和接收电路,用于高速、全双工的串行数据传输,传输速率高达6 Gbps。每个通道的PCS逻辑可以配置为支持一系列常用的数据协议,包括千兆以太网、XAUI、PCI Express PIPE、SRIO、CPRI、OBSAI、SD-SDI和HD-SDI。此外,基于协议的逻辑可以全部或部分绕过大量配置,使用户可以灵活地设计自己的高速数据接口。

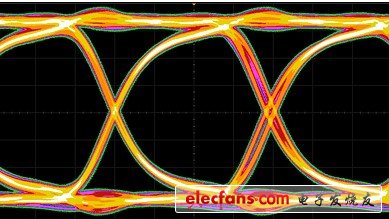

每个SERDES通道在6 Gbps下的功耗低于175mW,以最低功耗实现了高速串行协议。内置的预加重和均衡电路确保了低BER和高质量的眼图,如下图所示。

LatTIceECP4 SERDES特性和优点

多达16个通道的高速SERDES

每通道150 Mbps至6 Gbps数据速率

低功耗:每通道175mW@ 6 Gbps

内置预加重和均衡用于高级BER

清晰的SERDES眼图,低抖动

基于Quad的架构,可以在一个quad中混合匹配不同的协议

全功能嵌入式物理编码子层(PCS)逻辑支持业界标准协议

每个器件多达16个通道的全双工数据支持

一个芯片支持多种协议

支持常用的基于8b10b的数据包协议

SERDES Only模式允许直接8位或10位接口到FPGA逻辑

兼容CEI-6G

在低成本封装中实现6G SERDES的业界先锋

高价值、低功耗串行协议解决方案

下表总结了LatTIceECP4 SERDES支持的各种协议以及硬连线MACO通信引擎实现的协议处理。

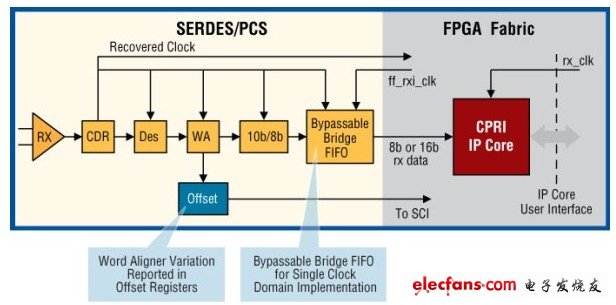

CPRI低延迟变化选项

物理编码子层(PCS)提供了一个低延迟变化选项,实现了更小、更简洁的CPRI。

查看评论 回复