Nios II嵌入式软处理器提升系统性能方式详解 - PLD开发板 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

电子发烧友网核心提示:Altera的嵌入式软处理器系列使您能够充分利用FPGA内在的并行优势,实现高级系统性能。多个处理器可以同时执行代码,而硬件加速器也能够同时卸载大计算量算法。不需要重新设计电路板或者手动优化汇编程序,便能够在产品生命周期的任何阶段更新嵌入式系统的性能。

以下介绍更新系统性能的几种方式:软核处理器;定制指令;硬件加速器;可配置高速缓冲和紧耦合存储器;多处理器系统;宽带系统互联。

方式1:软核处理器

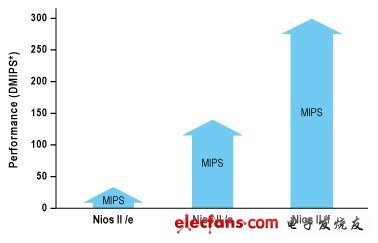

如果您使用Altera的Nios® II 处理器,可以从三种代码兼容的软核处理器中进行选择(参见图1):一种针对最佳系统性能进行了优化;一种针对最少逻辑占用进行了优化;还有一种是二者之间达到平衡。

采用乘法器、用户设定的高速缓存、定制指令、硬件调试逻辑等特性来配置这些内核,能满足用户的特殊性能需求。

图1. Nios II 处理器内核性能

详细了解【 Nios II 系列处理器内核 】

详细了解【 Nios II 系列处理器配置选项(PDF) 】

Altera嵌入式系列产品的其他软核处理器包括:

MP32处理器:业界第一款100%兼容MIPS®的软核处理器。

ARM® Cortex-M1处理器:三级32位ARM Cortex处理器。

Freescale V1 ColdFire处理器:具有全综合内核以及长度可调RISC 16位、32位和48位指令。

Intel® Atom® E6x5C处理器:在多芯片封装中组合了Intel Atom处理器E6xx系列以及Altera® FPGA。

查看评论 回复