实例详解:如何利用Zynq-7000的PL和PS进行交互? - FPGA/ASIC技

Zynq系列是赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。该系列四款新型器件得到了工具和IP 提供商生态系统的支持,将完整的 ARM® Cortex™-A9 MPCore 处理器片上系统 (SoC) 与 28nm 低功耗可编程逻辑紧密集成在一起,可以帮助系统架构师和嵌入式软件开发人员扩展、定制、优化系统,并实现系统级的差异化。

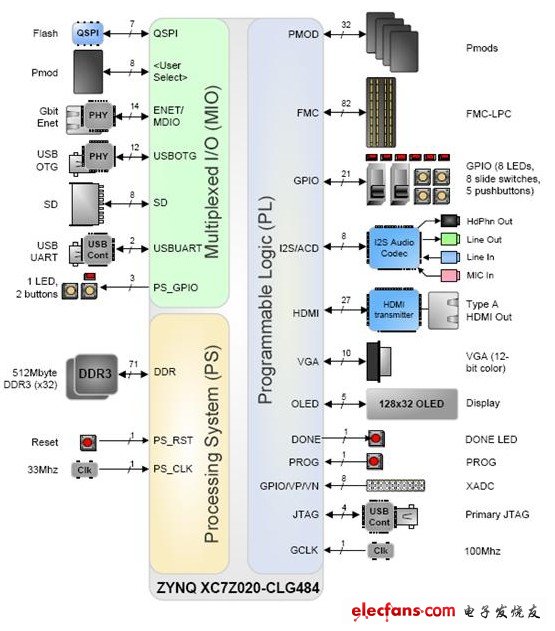

实际上,Zynq就是两大功能块:双核Arm的SoC和FPGA。根据Xilinx提供的手册,PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。这有点像xilinx以前推出的powerPC+FPGA平台。下图为官方文档中介绍的ZYNQ内部结构。

从图中可以看到,ZYNQ的绝大多数外设都是PL逻辑部分相连,比如说GPIO,IIS,XADC等等,所以如果我们要使用这些外设的话必须在PL逻辑部分对其进行配置。OK,下面我们就以一个简单的例子来看看如何使用PL和PS进行交互。在下面的例子中,我们通过设置8个开关来对应点亮8个LED灯。

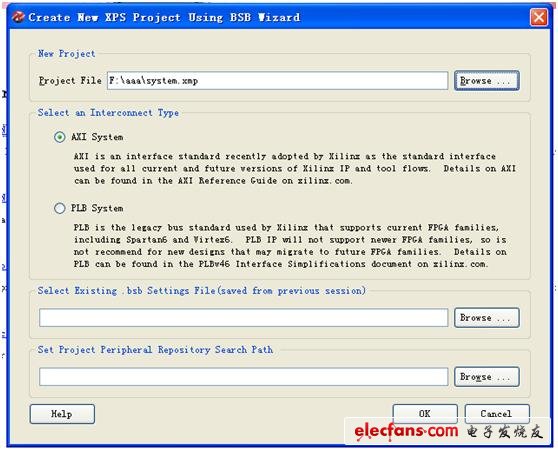

首先打开XPS,由于XILINX内部已经帮我们做好了GPIO部分的IP核,所以我们只需要直接使用即可(如果要用自己的ip核,则可以使用ISE先把IP核写好再导入进来)。新建立一个工程,选择“Create New Project Using Base System Builder”,

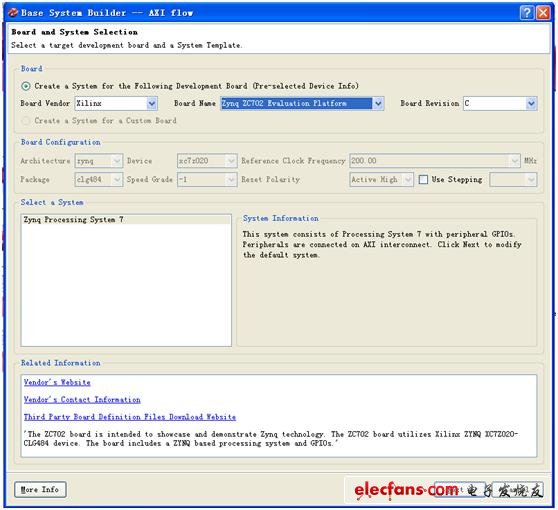

填好项目工程文件的路径,其它不需要更改,直接点OK,出现如下界面:

查看评论 回复