DDR布局方法对比 - FPGA/ASIC技术 -

来源: 网络用户发布,如有版权联系网管删除 2018-08-18

点对点的拓扑结构布局: (处理器或者FPGA外接一颗芯片)

内存芯片尽量靠近控制器

串联匹配电阻靠近控制器放置

并联匹配电阻靠近内存芯片

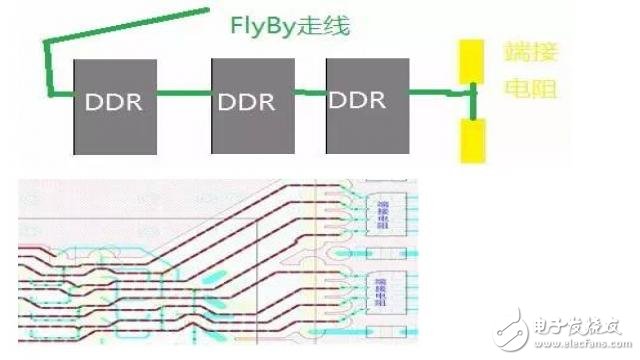

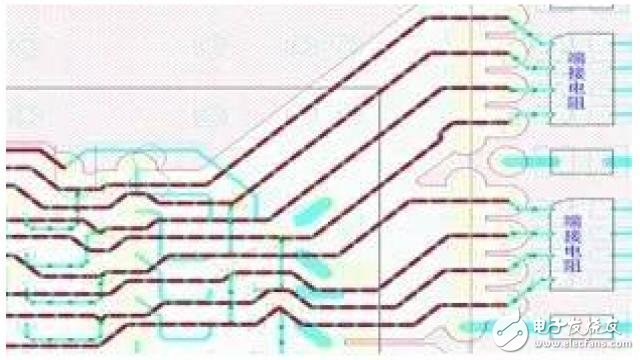

一驱多的拓扑结构布局:

(1) 内存芯片贴在同一面。建议fly-by拓扑,并联匹配电阻放置在最后一个内存芯片的末端。

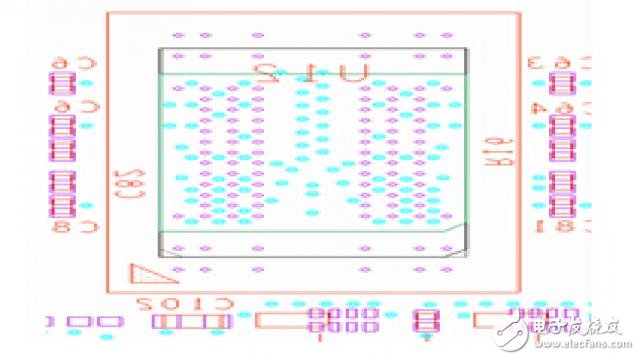

(2)两个内存芯片完全对贴 。两片内存芯片信号质量一样且信号质量最好,最节省空间,这种完全对贴的设计在DIMM上已经很成熟的应用。 在T点采用VTT上拉。

但是两个内存芯片完全对贴,两个DDR的热量在同一个点进行叠加。热量比单芯片高一些。如果环境温度比较恶劣,可能会超过芯片规格。

(3)错位的正反贴布局方式。能节省一部分空间,走线方法简单,可测试性较好。末端匹配电阻需要放置在最后一个内存芯片后边。从空间节约效果上来说不如“正反对贴”

查看评论 回复