基于FPGA和IQ调制器的能量倍增器系统设计 - FPGA/ASIC技术 -

摘 要:介绍了基于可编程逻辑门阵列(FPGA)的能量倍增器(SLED)相位翻转系统。该系统主要由微波IQ调制器、FPGA 和高速DAC 组成。在FPGA 的控制下,DAC 输出两路双极性脉冲电平信号,加载于调制器的IQ 端,将微波连续波输入信号转变为4μs脉冲输出信号,并且在3μs时刻微波相位发生180°跳变。经测试,相位翻转精度为180°±2°,翻转相位的长期稳定度优于±0.5°;相位翻转系统驱动的6台SLED 的输出功率增益均超过7dB,最高达到7.54dB,增益的长期稳定度达到±0.1dB。

在合肥光源(HLS)重大升级改造工程中,为了实现储存环满能量注入,直线加速器的能量从200MeV 升级到800MeV。速调管功率源从5个增加到8个,其中80 MW 速调管2个(1#,8#),50 MW 速调管6个(2#~7#)。每个速调管驱动2根3m 等梯度加速管,构成一个加速段。2#~7# 微波系统中安装了能量倍增器(SLED),全部启用可将电子能量提高到1GeV。能量倍增器是一种RF脉冲能量压缩装置,可将RF长脉冲压缩为高峰值的短脉冲。能量倍增器工作时,输入微波信号需要在脉冲内进行快速相位翻转,为此我们研制了基于FPGA 和IQ调制器的相位翻转系统。

1 能量倍增系统的总体参数设计

HLS的SLED是由中国科学院高能物理研究所研制,主要技术指标见表1。6台SLED和低电平相位翻转系统的布局如图1所示。

图1 800 MeV 直线加速器布局图

HLS SLED设计为将4μs功率脉冲压缩为1μs,即速调管输出3μs脉冲功率后,微波相位立即跳变180°,并持续1μs。在两个储能腔调谐一致和微波相位翻转180°的理想状态下,SLED的理论设计增益可达到7.8dB。依据800MeV 直线加速器的总体设计方案,SLED的增益指标为不低于7dB,增益设计值与实际工作值之间有较大余量,因此可适当放宽相位翻转系统的绝对精度要求。但为了保证脉冲间直线加速器电子束能量的一致性和稳定性,相位翻转必须在脉冲间保持高度的一致。相位翻转系统的基本设计指标为:相位翻转精度为180°±2°,翻转相位的长期稳定度为±0.5°。整个能量倍增系统的考核指标为:峰值能量增益大于7dB,增益的长期稳定度达到±0.1dB。

2 相位翻转系统结构设计

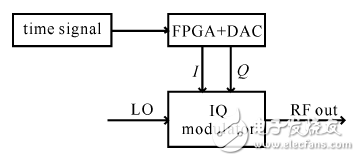

相位翻转系统主要由IQ 调制器、FPGA 功能板和光电转换模块组成,如图2~3所示。

图2 相位翻转系统原理图

图3 相位翻转系统实物图

国内外相关实验室的相位翻转系统普遍采用PSK(phaseshiftkeying)开关或跳相控制电路作为跳相执行器件[7-9],我们选择IQ 调制器,主要原因是它有同相(I)和正交(Q)两个控制信号,有生成复杂幅相调制模式的潜力;其次,当IQ 信号幅度为零时,调制器的射频输出是截止的,可用于整个直线加速器装置的快速联锁保护[10]。IQ 调制器采用了Pulsar Microwave公司的IDOH-01-45,其LO 载波频率为2~4GHz,通道带宽为100MHz,IQ 幅度、相位稳定度分别优于为1dB和8°,通道隔离度为30dB,驻波比小于1.5。光电转换模块接收来自于加速器时序系统的光脉冲信号,转换为电信号输入FPGA 单元,作为触发信号。FPGA 系统采用一块Xilinx-Vertex5的FPGA 开发板搭配高速可扩展ADDA 板。FPGA 内部锁相环倍频模块(PLL)最高可产生200MHz的时钟信号,为保证FPGA 时序稳定性,将内部时钟设定为100MHz。高速ADDA 扩展板在Vertex5FPGA 平台上可实现14位的模数、数模转换。图4为FPGA 和DAC的功能框图。

图4 FPGA和DAC功能框图

利用硬件描述语言(VerilogHDL语言)在ISE软件开发环境下,调用FPGA 内的相关模块如PLL模块、DAC模块、BUFER模块等编写了相位翻转信号的逻辑控制程序。DAC脉冲输出信号的生成采用了FPGA的状态机模式。无触发信号时,FPGA 状态机处于0状态,写入高速DAC板的值保持为0;受到高电平触发后,FPGA 开始执行内部时钟为100MHz的状态机,以100MHz的数据刷新率将编辑好的赋值表写入DAC板,输出两路脉冲电平信号,赋值表写完后状态机回归0状态。

查看评论 回复