视觉系统需要更快更高级的处理以及更严格的时序与同步 - FPGA/AS

NI 的视觉开发模块和视觉助手让机器视觉从构思到原型再到应用部署一路通畅。

视觉系统正在成为主流。技术的成本/效益分析及合理应用已发展到这样的阶段: 工程师正在将视觉功能运用到各种应用中,从无人驾驶汽车到消费类电子产品质量检测系统无所不包。这种大规模采用正在推动视觉走出实验室,走进嵌入式系统和工厂车间。所部署的系统往往需要与控制环路中的 I/O、广泛分布的大量摄像头或视觉功能实现高级同步。随着工艺和应用的日趋复杂化,视觉系统正在要求更快、更高级的处理以及更严格的时序与同步。

为满足这些要求,视觉系统设计人员正日渐依赖由实时处理器、FPGA、GPU 或 DSP 处理单元构成的异构处理平台处理专门的任务,满足 I/O要求和处理性能需求。智能相机、图像采集卡和视觉系统都使用异构架构来满足应用要求。

FPGA 具备的并行处理功能,例如赛灵思 All Programmable FPGA 系列提供的并行处理功能,自然适用于实现大量图像处理算法的。FPGA 可用于同时执行高数据强度处理和高速传感器测量。此外,这类器件时延极低,这对视觉应用来说极为重要,因为时延会增大根据图像数据做出决策所需的时间。FPGA 有助于避免抖动,因此可作为高确定性的处理单元。

但是构建包含一个 FPGA 的异构系统会给系统设计人员带来严重的编程难题。在上市时间的重压下,视觉系统设计人员要能够迅速构建具有复杂特性的解决方案原型。在异构系统上编程需要这样一种工具: 在目标硬件上编译和运行算法之前,其不仅可帮助领域专家在多个平台上设计 IP 功能,而且还可帮助他们测试视觉算法。该工具应该支持: 在整个原型设计过程中能够轻松访问吞吐量及资源使用信息。

NI 把这称之为算法工程。采用该工艺技术,领域专家,可集中精力解决手里的难题,不必关注底层硬件技术。NI 具有视觉助手的视觉开发模块 (VDM) 能够为您提供支持视觉助手的视觉开发功能。

配备视觉助手的 VDM 有助于快速完成原型设计、代码生成、FPGA 资源估算、自动代码并行化以及并行数据流同步化(针对时延均衡等任务)。VDM 包含超过 50 种 FPGA 图像处理功能以及在处理器与 FPGA 之间高效传输图像的功能。您可使用 VDM 中的视觉助手迅速设计 FPGA 视觉应用原型,开发 FPGA 视觉应用。

基于配置的原型设计

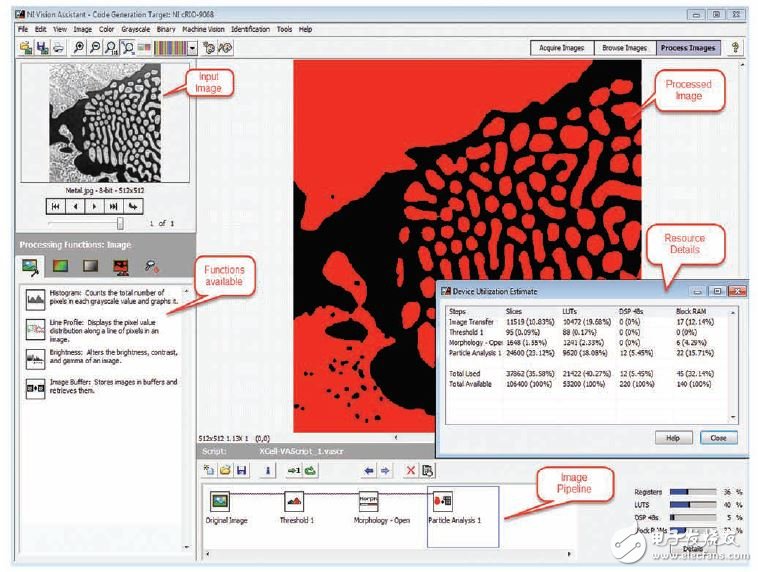

视觉助手是一种基于配置的原型设计工具,可帮助您迭代图像处理算法,查看参数调整如何影响图像。有了视觉助手,您可以在图像流水线中的每一个视觉模块后显示输出(处理后的图像)(图 1)。您可使用该工具测试不同图像集上的不同算法和参数,无需编译 IP,因此可显著减少设计视觉算法所需的时间。

图 1 — 能够估算器件利用率的视觉助手

您可使用视觉助手测试原型设计环境中算法的结果和所部署代码的结果,以确保实现方案可获得相同的结果。

NI 已经定制了用于满足 FPGA 编程人员要求的工具。在 FPGA 上构建任何算法时,主要考虑因素是 FPGA 架构上的资源消耗、流水线的时延以及在特定架构上该算法可实现的最高频率。视觉助手通过为图像流水线中的每个模块提供所消耗资源的估算,起到帮助作用。您可使用该工具测试原型设计环境中算法的结果和所部署代码的结果,以确保实施方案能够获得相同的结果。

一个考虑因素是把多大的内核用于图像滤波运算。内核大小的选择会影响流水线中资源的使用和时延情况,较大的内核一般比较小的内核需要的资源更多。

要为应用选择最合适的内核大小,您可使用视觉助手进行实验,直到您在最小资源耗用和最大性能方面取得最理想的结果。如图 1 所示视觉 IP 功能实时估算是原型设计过程中的一个必备功能。

视觉开发模块的视觉 FPGA IP可让开发人员使用大规模并行处理和 Vivado 高层次综合工具在 FPGA 上实现全面流水线的低时延架构优化型视觉功能。