基于XVC网络协议实现了基于JTAG接口的FPGA 的远程更新与调试 - F

摘要:同步辐射光源硅像素探测器是面向北京先进光源对X 射线探测的重大技术需求所研发的新型仪器。该探测器处于辐射环境中,且多个前端电子学读出板被放置在密封的冷却容器中。为在不打开冷却容器的情况下,脱离专用的USB-JTAG (Universal serial bus - joint test acTIon group)下载电缆对现场可编程门阵列(Field programmable gate array, FPGA)进行远端升级,本文提出了一种基于XVC (Xilinx visual cable)协议,通过以太网,利用ARM 微控制器控制FPGA 的JTAG 接口对其进行远程更新与调试的方法。该方案附加电路少,易于拓展,同时也提高了更新可靠性。

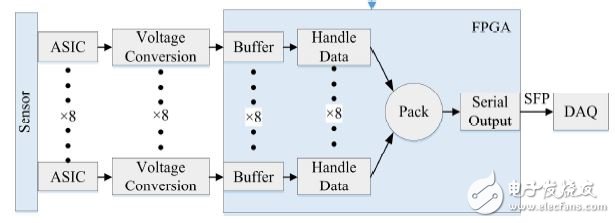

前端探测器包含6 个前端模块,每个模块对应一个传感器以及8 个读出ASIC 芯片,芯片输出信号通过电平转换送到前端数据处理现场可编程门阵列(Field programmable gate array, FPGA)。FPGA 对信号进行缓冲验证,汇总处理后通过光纤传输到后端DAQ (Data acquisiTIon)系统。图1 为前端数据处理框图。

图1 前端数据处理框图

由于整个前端探测器模块放置在密封的冷却容器中,而且整个探测器处在辐射环境中,方便可靠的FPGA 远程更新与调试方案成为电子学系统设计的重要方面。显然传统的基于USB-JTAG (Universalserial bus - joint test acTIon group)更新FPGA 的方式已不再适用。

目前国内外出现的FPGA 远程更新的方案基本分为两大类[2]:一类是针对早期的内部没有专用远程升级电路的FPGA 器件,采用单片机CPLD(Complex Programmable Logic Device)、DSP (Digital Signal Processor)、ARM (Acorn RISC Machine)等作为辅助配置器件[3],配合外部Flash 和以太网芯片来实现,这些方案灵活性高但设计复杂且提高了成本;另一类是针对最新推出的FPGA 器件,其自带了远程升级内核或逻辑块,只要结合外部数据配置通道,即可实现远程更新,该方案附加电路少,节省硬件资源,但却占用了FPGA 的内部逻辑资源,而且只适用特定型号的FPGA。另外,上述两类方案均无法实现对FPGA 的远程调试,还需要在PC 端开发用于远程更新的TCP/IP 软件,增加了设计复杂度。考虑到基于JTAG 的下载方式在FPGA 配置、Flash PROM 配置、软/硬件调试以及硬件测试方面的重要用途,本文设计了一种基于XVC (Xilinx visual cable)协议,通过以太网,使用单芯片ARM微控制器控制FPGA 的JTAG 接口进行远程更新调试的方案。该方案操作简单,无需额外开发TCP/IP软件,基于网络的通信能够保证足够远距离的灵活的可靠数据传输。还能对FPGA 进行远程ChipScope调试。同时,通过简单的JTAG 链路连接,可以同时完成多片FPGA 的升级与调试[4]。

1 硬件系统实现

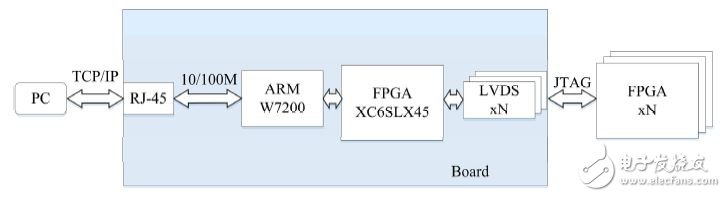

在本设计中,ARM 微控制器通过模拟JTAG 接口的时序对FPGA 进行配置。针对多片FPGA 进行远程更新的系统框图如图2。

图2 系统模块框图

系统硬件电路主要由ARM 微控制器、JTAG 链路模块、LVDS (Low-voltage differenTIal signaling)模块组成。ARM 选择Wiznet 公司的W7200 开发板作为配置控制器,一端通过网络与PC 建立连接,另一端通过外设的GPIO (General purpose input output)传输JTAG 配置时序。LVDS 模块负责将JTAG 单端信号转换为低压差分对信号,一对一发送给待更新的FPGA。多片待更新FPGA 的JTAG 链通过另外一块FPGA 开发板上的主控FPGA 芯片XC6SLX45的内部逻辑来实现,板上用9 个接插件引出FPGA的9 组I/O,分别连接W7200 和8 个LVDS 模块。其中, LVDS 模块和主控FPGA 开发板以子母板的形式连接。

远程更新时,PC 端使用iMPACT 将包含配置的指令通过网络发送给W7200,W7200 根据XVC 协议接收指令并模拟产生JTAG 时序,主控FPGA 接收该时序并通过JTAG 链路送入待配置FPGA,完成最终配置。

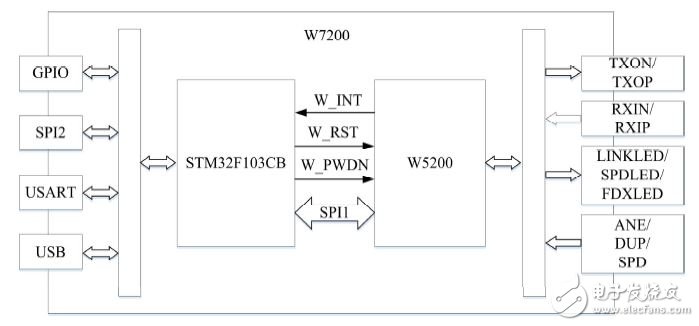

W7200 是Wiznet 公司推出的一款单芯片集成了硬件TCP/IP 协议栈的ARM Cortex-M3 微处理器[5]。内有20 KB 的SRAM 和128 KB 的Flash 以及32 KB 的以太网RX/TX 缓存,具有最高72 MHz的工作频率,有足够的能力进行数据处理。硬件TCP/IP 协议支持 TCP、UDP、IPv4、ICMP、ARP、IGMP、PPPoE 和以太网,这些协议在各种应用领域已经得到多年的验证。其结构如图3 所示。

图3 W7200 结构框图

查看评论 回复