����FPGA���������ߵ��ز�ͬ�����������ʵ�� - FPGA/ASIC���� -

ժ��Ҫ��ͬ��ϵͳ�����ĺû����ںܴ�̶��Ͼ�����ͨ��ϵͳ��������GPS���ջ������߽��յ��������źž���Ƶǰ�˴���������������Ƶ�źţ����ջ���GPS���ǵ��źŴ������̣������η�Ϊ�����١�λͬ����֡ͬ���ĸ��Ρ����GPS�źŵ�BPSK���ƺ�ǿ�������ص㣬ģ��GPS ���ջ����������źŴ������̣����Ƚ����˿�˹��˹��Costas�����ջ��Ĺ���ԭ���������о��˻���FPGA���������ߵ��ز�ͬ��������ʵ�ַ�����������Costas ��ʵ�����ز�ͬ�������ܲ�����֤����Ƶ���ȷ�ԺͿ����ԡ�

���ջ���GPS���ǵ��źŴ������̣��������η�Ϊ�����١�λͬ����֡ͬ���ĸ��Ρ�����λͬ����֡ͬ������Ҫ�����ݽ��Ϊǰ�����������˷��ȵ��Ƽ�Ƶ�ʵ��ƿ��Բ��÷���ɽ���⣬�ֵ��Ʒ�ʽ��������ɽ���Ի�ȡ���õ����ܣ���������ɽ�������ն˾ͱ�����ȡ����ز����ز�ͬ��������ֱ��Ӱ����ͨ��ϵͳ�����ܡ����GPS�źŵ�BPSK ���ƺ�ǿ�������ص㣬GPS ���ջ����ͨ������I/Q �������������ɶ������źŵ��±�Ƶ����������ݽ����������ͬ�����ǹ����Ϲ㷺Ӧ�õ�һ���ز�ͬ����ʽ����ͬ������Ҫ�������ƽ������Costas�����о��������ȡ�Ŀǰ��������õ������ز����ٻ���ƽ������Costas���ȡ�����Costas ������Ҫ�Խ����źŽ���ƽ���任��Ҳ����Ҫ�����·��DDS ������ز��źŽ��з�Ƶ���������ʵ�ָ��Ӷȸ�СЩ�����ķѵ�Ӳ����ԴҲ���١�ģ��GPS ���ջ����������źŴ������̣����Ƚ����˿�˹��˹��Costas�����ջ��Ĺ���ԭ���������о��˻���FPGA ���������ߵ��ز�ͬ��������ʵ�ַ�����������Costas ��ʵ�����ز�ͬ�������ܲ�����֤����Ƶ���ȷ�ԺͿ����ԣ���ʵ��Ӧ�þ���һ����ָ����ֵ��

����Costas���ջ��Ĺ���ԭ��

Ŀǰ���ز�ͬ�������ж��ֵ�·��������õ���ƽ������Costas ����ͬ��D�����������о��������ȡ�J.P. Costas�ڣ������� �������������ͬ��D���������ָ��ز��źţ����Riter ֤�����ٵ�����ȵ������ز��źŵ����װ����Costas ����ƽ��������ͳ��ģ��Costas �������ͬ��֧·������֧·�IJ�ƽ���ԴӶ�ʹ��·�������ܵ�һ��Ӱ�죬��ģ���·������ֱ�����Ư�ơ����Ե��Ե�ȱ�㣬������ȫ���ֵ�ʵ�ַ�ʽ���������Ч������Щ���⡣

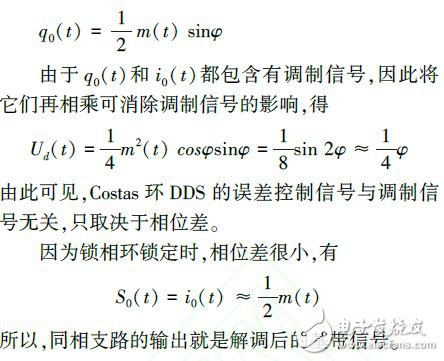

Costas���Ĺ���ԭ����ͼ�� ��ʾ����Ҫ������Ƶ�ʺϳ�����DDS�������ּ��������˷�������α�뷢������pn_gen������ͨ�˲�����LPF �ͻ�·�˲�����LF����ɡ����������������źŷֱ����ͬ���������·�ز��źţ���˳������ֻ�·Ϊͬ��D����������ƿ�˹��˹����Costas���������źž��ϡ���֧·�ֱ����ͬ��������ز���Ȼ������α�������ˣ���ͨ����ͨ�˲���������ˣ���ɼ���ܣ����·�˲���������Ʊ�������������ѹ��

����ϵͳ�����ʵ��

������������ѡȡ

ȫ�����ز���ϵͳ����������£�

�������ʣ����ͣȣ���α�����ʣ�10�ͣȣ���

�ز�Ƶ�ʣ�70�ͣȣ���ϵͳʱ�ӣ���00�ͣȣ���

��Ƶ��������ز�Ƶ�ʣ�6�ͣȣ���

�ŵ�������20�ͣȣ������Ʒ�ʽ��BPSK��

��������ϵͳ���

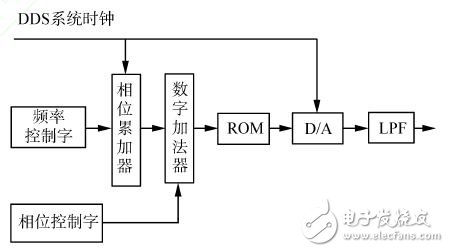

����ֱ������Ƶ�ʺϳ����������ʵ��ֱ������Ƶ�ʺϳ����Ļ�������ԭ����ͼ��ͼ�� ��ʾ��

ͼ�����ģģ� ��������ԭ����ͼ

ֱ������Ƶ�ʺϳ�����direct digital frequency synthesizers,DDS�����ڲ���Ƶ�ʼ���λ�ɿص����������źš�DDS �Ļ�������ԭ������ʱ���źŵ������¶�ȡ���Ǻ���������FPGAʵ���У�ͨ������ISE�����ṩ��DDS ����ʵ�֡�

�������������������������� �鿴���� �ظ�

"����FPGA���������ߵ��ز�ͬ�����������ʵ�� - FPGA/ASIC���� -"���������

��������

- Xilinx FPGA�ڻ���������е����� - FPGA/ASIC���� -

- ����CPU���ģ������д

- ����FPGAоƬ�Ĺ��£���֪�������أ� - �ɱ���� -

- Mellanox����Ƕ��Xilinx FPGA,��ʵ�����繦������ -

- ��˼�Ƽ���������Cortex-A76��Mali-G76���������ڵ�Ar

- ����˼�뵼���Ƴ�ȫ�µ�ģ�黯IP�ˣ���Ϊ�ͻ��ṩ����

- FPGA��Ʒ��������������˼����ս�����������г����� -

- ����FPGA�����ѧϰ�Ĺ�ϵ̽����� - �ɱ���� -

- ���ΪAI�����ޣ�������FPGAΪ����֧�� - �ɱ����

- SDSoc��������-ʹ��MIO����LED - �ɱ���� -