谈JTAG to AXI Master对于系统的控制和调试 - FPGA/ASIC技术 -

在一个SOC系统中,通常会有CPU,各种总线,以及各种各样的外设,接口等模块,以及运行在CPU上的软件系统(裸跑或者带操作系统)。这样的系统,通常调试起来都会比较费时费力,不论是对硬件还是软件调试来说,都是如此。

作为硬件或者逻辑工程师,在调试的初期,可能还不得不涉及到很多软件调试代码的编写工作,以辅助验证基本逻辑功能模块的正确性。如果工程师对软件或者C不熟悉,那么实在是一件非常痛苦的工作。那么有没有一种手段,能够适当减轻这些调试为目的的软件代码的编写工作呢?

答案是存在的,JTAG to AXI Master就是这样一个非常有用的IP,我们只需要在系统里面把它集成进去,在板级调试时,就可以通过JTAG端口,通过tcl命令来读写操作各个AXI Slave模块的地址空间。

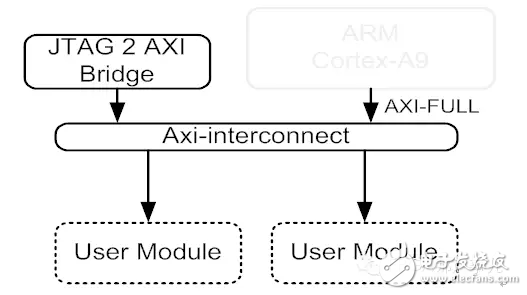

通常集成JTAG to AXIMaster Beidge的系统是如下样子的:

在调试一个集成了JTAG to AXIMaster的系统时,可以直接通过tcl命令去读写AXI外设的地址空间。以下是一个tcl 命令片段示例:

reset_hw_axi [get_hw_axis hw_axi_1]

set wt [create_hw_axi_txn write_txn [get_hw_axishw_axi_1] -type WRITE -address 00000000 -len 128 -data{44444444_33333333_22222222_11111111}]

set rt [create_hw_axi_txn read_txn [get_hw_axishw_axi_1] -type READ -address 00000000 -len 128]

run_hw_axi $wt

run_hw_axi $rt

上述命令,首先复位JTAG to AXI模块,然后创建了一个4word宽度,128length的写命令wt,和一个128length的读命令,然后分别执行2个命令。如果读写的区域是一片RAM,那么读回的数据应该和写入的是一致的。

查看评论 回复