FPGA仿真篇_使用脚本命令来加速仿真 - FPGA/ASIC技术 -

1.背景知识

FPGA的仿真与调试在FPGA开发过程中起着至关重要的作用,也占用了FPGA开发的大部分时间。所以适当减少或简化FPGA的仿真与调试过程无疑是对FPGA开发的加速,所对产品成型的时间。这里我们将利用三篇给大家讲解使用脚本命令来加速FPGA的仿真过程。

FPGA的仿真又分为前仿真和后仿真,前仿真即功能仿真,是在不考虑器件的布局布线和延时的理想情况下对源代码进行的仿真;后仿真即时序仿真,时序仿真主要在布局布线后进行,与特定的器件有关,在仿真时还要包含器件和布线延时信息。

FPGA的仿真工具也很多,其中用各公司软件自带的仿真工具,也有其他公司的仿真工具。其中Mentor公司的Modelsim是业界比较优秀的仿真软件,它提供了友好的仿真界面。

本次使用xilinx的官方例程xapp859来为大家做实验,xapp859是一个PCIE,dma,DDR2控制器,以及DDR2的较大工程。对于要学习PCIE,DMA的同学具有很大帮助。其中工程中使用到了大量xilinx IP,也是对《FPGA仿真篇-使用脚本命令来加速仿真一》的进一步补充和讲解。

2.使用脚本语言命令加速仿真

Xapp859这个例程我会在QQ群里边给出,或者大家自己去xilinx官网下载。

图1 xapp859

图1给出了整个文件的子目录。其中doc文件夹中有详细介绍xapp859工程的pdf文件,有兴趣的同学可以重点看一下。

图2 xapp859子文件夹

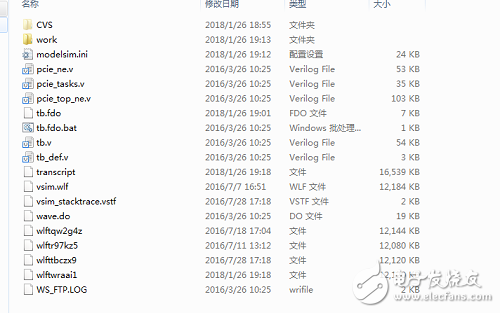

图2是xapp859\fpga\simulaTIon\funcTIonal子文件的截图,我们所需要的重点仿真脚本文件都在这里。

图3 tb.fdo.bat

图3是.bat文件,双击此文件整个工程就可以运行。

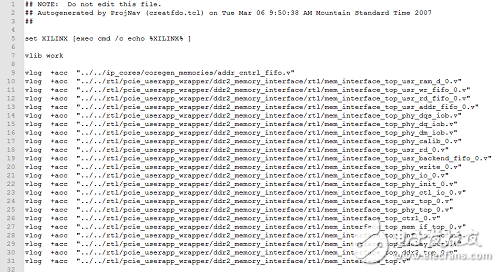

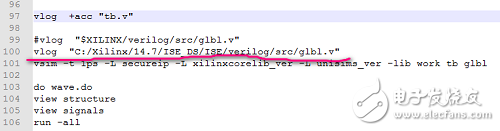

图4 tb.fdo

图4 是tb.fdo文件里边是我们重点学习的脚本语句,如何增加verilog文件,大家一看便知。

图5 wave.do

图5 为wave.do文件,这个文件被tb.fdo文件调用,主要是增加波形信号。

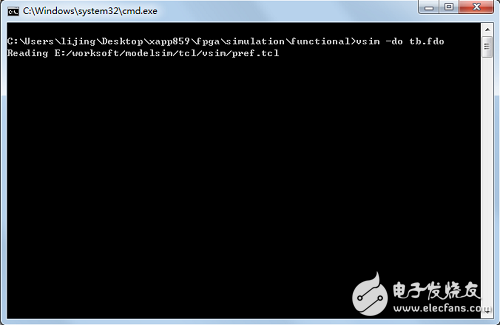

图6.bat启动

图6 为双击xapp859\fpga\simulaTIon\funcTIonal目录下的tb.fdo.bat运行后的结果,它会自动启动modelsim软件。

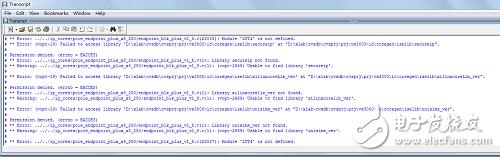

图7 运行过程中碰到的第一个错误

图7,为运行过程中的第一个错误# ** Error: (vlog-7) Failed to open design unit file "%XILINX%/verilog/src/glbl.v" in read mode.修改到你的正确路径。例如图8。

图8修改后的tb.fdo

图9 运行中的第二个错误

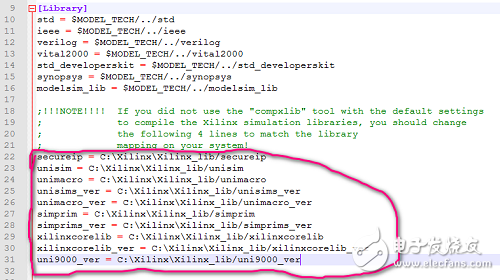

图9 使我们运行过程中的第二个错误,这是因为IP的仿真库找不到。修改xapp859\fpga\simulation\functional路径下modelsi.ini如下图10。

图10 修改后的modelsim.ini

图10,是xilinx生成的仿真库,我们自己要保证路径正确。

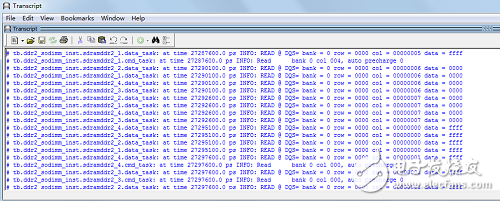

图11Transcript 显示脚本运行成功

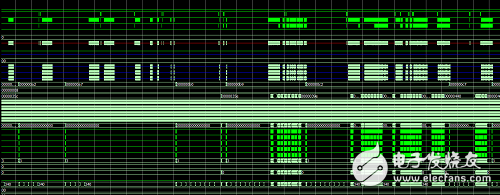

图12 最后波形的输出

查看评论 回复