S3C2416裸机开发系列六_MMU映射 -

[导读]S3C2416带有CP15协处理器,里面集成了16KB的I/D-Cache和MMU。MMU负责虚拟地址到物理地址的映射,并提供硬件机制的内存访问权限检查。笔者此处就MMU的使用作一个简单的介绍。1. MMU映射时存储器访问ARM CPU使用表格存

S3C2416带有CP15协处理器,里面集成了16KB的I/D-Cache和MMU。MMU负责虚拟地址到物理地址的映射,并提供硬件机制的内存访问权限检查。笔者此处就MMU的使用作一个简单的介绍。

本文引用地址: http://www.21ic.com/app/mcu/201808/784299.htm

1. MMU映射时存储器访问ARM CPU使用表格存储虚拟地址对应的物理地址,这类表格称为页表,页表由一个个条目组成,每个条目存储了一段虚拟地址对应的物理地址及其访问权限,或者下一级页表的地址。

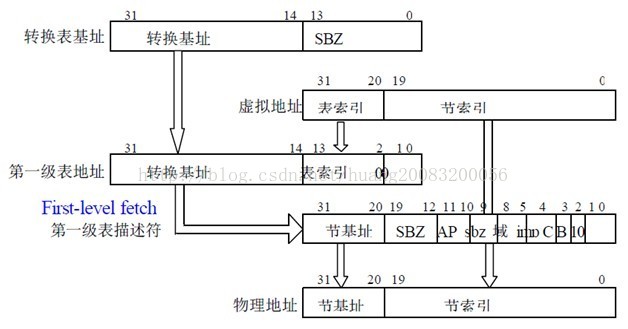

当ARM要访问存储器时,根据MMU设定的一级页表基址(16KB对齐)以及虚拟地址一级页表索引[31:20],产生一个第一级描述符地址。MMU先查找TLB(转译查找缓存)中的虚拟地址表,如果是取指,则用指令TLB,否则用数据TLB。TLB的作用就是缓存之前遍历使用过的页表条目,避免每一次地址转换都去主存页表查找对应的条目,不然性能无法忍受。如果TLB中有第一级描述符地址的入口,则可直接得到该虚拟地址对应的一级页表描述符。描述符包括了访问权限、域、高速缓存、转换基址(二级页表基地)等信息。如果TLB没有第一级描述符地址的入口,则转换表遍历,硬件从主存储器转换表中获取对应的条目,并放入到TLB中。

S3C2416最多会使用到两级页表。以段(1MB)的方式进行转换时只用一级页表,以页方式进行转换时用到两级页表。页的大小有3种,分大页(64KB)、小页(4KB)、微页(1KB)。

当从TLB得到的一级页表描述符为段描述符时,从描述符中可以直接得到这段的段转换基址(1MB对齐),域和权限访问,高速缓存的信息。根据段转换基址以及虚拟地址[19:0]可以得到对应要访问的物理地址。

图1-1 访问段描述符

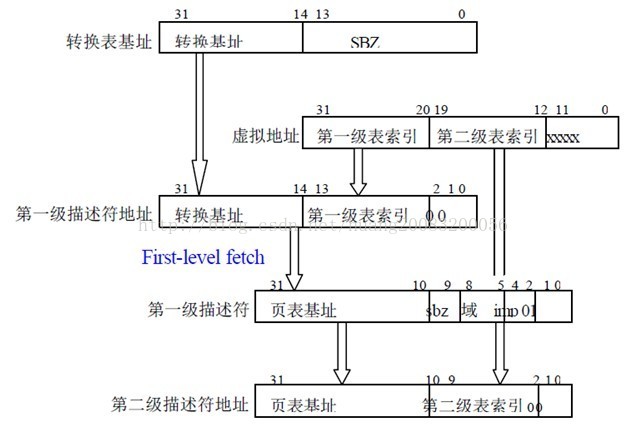

当从TLB得到的一级页表描述符为粗页描述符时,从描述符中直接得到粗页表的基址(1KB对齐),域访问信息。粗页表每个条目表示4KB的物理地址空间。根据粗页表基址以及虚拟地址粗页表索引[19:12]可以得到第二级描述符地址,从而得到第二级页表描述符。第二级页表描述符可以直接得到大页、小页或微页中三者之一的页基址,访问权限,高速缓存控制信息。根据页基址以及虚拟地址[11:0]得到对应要访问的物理地址。

图1-2 访问粗页第二级描述符

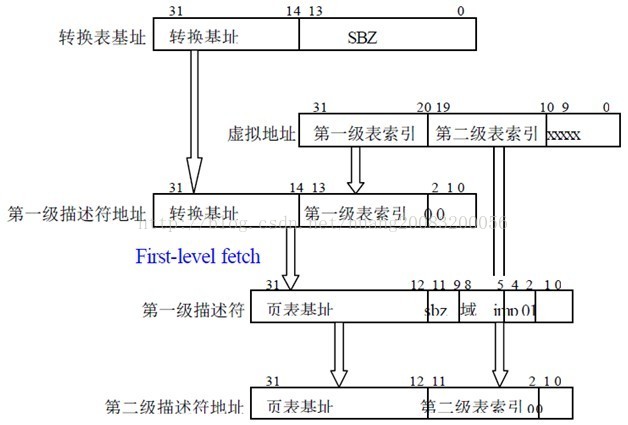

当从TLB得到的一级页表描述符为细页描述符时,从描述符中直接得到细页表的基址(4KB对齐),域访问信息。细页表每个条目表示1KB的物理地址空间。根据细页表基址以及虚拟地址细页表索引[19:10]可以得到第二级描述符地址,从而得到第二级页表描述符。第二级页表描述符可以直接得到大页、小页或微页中三者之一的页基址,访问权限,高速缓存控制信息。根据页基址以及虚拟地址[9:0]得到对应要访问的物理地址。

图1-3 访问细页第二级描述符

2. Cache一般而言,存储器对于cpu来说都是慢速设备。如果每次取指或读写数据都去访问主存储器,则cpu必须等待主存储器读取完成才能进一步往下处理,性能无法忍受。笔者测试相同代码开了Cache与不开Cache,性能有天壤之别。Cache就是在主存与cpu通用寄存器间设置的一个高速,但容量较小的存储器。它能够缓存部分之前执行的代码(或读取的数据)以及目前正在执行的这段代码(或读取的数据)。开启了Cache后,当cpu需要取指(或读取数据),如果Cache中有缓存,则直接从Cache中获取返回,否则访问主存储器。由于程序访问的局部性,Cache具有很高的命中率,对提高程序的运行性能有很大的作用。

3. MMU映射代码实现在嵌入式设计中,一般为了提高性能,是需要开启MMU的,对开D-Cache,是必须在MMU开启后才能使用。S3C2416从IROM SD/MMC启动时,ARM 0x0偏移处异常向量表位置是内部固化代码地址。如果不对0x0处地址进行内存映射,则无法使用中断。我们采用段方式进行映射,每个条目对应1MB的物理地址空间,32位地址空间共需4096条条目,即需16KB的页表内存空间。我们实现的MMU模块头文件MMU.h内容如下:

#ifndef__MMU_H__

#define__MMU_H__

#ifdef__cplusplus

extern"C" {

#endif

// ICache使能控制位

#define R1_I (1<<12)

// DCache使能控制位

#define R1_C (1<<2)

// 地址对齐检查使能控制位

#define R1_A (1<<1)

// MMU使能控制位

#defineR1_M (1<<0)

// 段标识符,以段(1MB)方式进行映射

#define DESC_SEC ((1<<1)"(1<<4))

// cache_on, write_back cache会出现命中的情况

#define CB (3<<2)

// cache_on, write_through

#define CNB (2<<2)

// cache_off,WR_BUF on cache不会出现命中的情况

#define NCB (1<<2)

// cache_off,WR_BUF off

#define NCNB (0<<2)

//supervisor=RW, user=RW

#define AP_RW (3<<10)

//supervisor=RW, user=RO

#define AP_RO (2<<10)

//supervisor=RW, user=No access

#define AP_NO (1<<10)

// 任何访问都将导致"Domain fault"

#defineDOMAIN_FAULT (0x0)

// 使用描述符中的设置进行权限检查

#defineDOMAIN_CHK (0x1)

// 不进行权限检查,允许任何访问

#define DOMAIN_NOTCHK (0x3)

// 在域0检查权限

#define DOMAIN0 (0x0<<5)

// 在域1检查权限

#define DOMAIN1 (0x1<<5)

// 域0属性为用描述符权限进行权限检查

#defineDOMAIN0_ATTR (DOMAIN_CHK<<0)

// 域1属性为不可访问

#defineDOMAIN1_ATTR (DOMAIN_FAULT<<2)

// 段描述符域0可读写,开cache 写缓存

#define RW_CB (AP_RW|DOMAIN0|CB|DESC_SEC)

#defineRW_CNB (AP_RW|DOMAIN0|CNB|DESC_SEC)

#defineRW_NCB (AP_RW|DOMAIN0|NCB|DESC_SEC)

#defineRW_NCNB (AP_RW|DOMAIN0|NCNB|DESC_SEC)

// 段描述符域1不可访问

#defineRW_FAULT (AP_RW|DOMAIN1|NCNB|DESC_SEC)

void MMU_EnableICache(void);// 使能ICache

voidMMU_DisableICache(void); // 禁止ICache

voidMMU_EnableDCache(void); // 使能DCache

voidMMU_DisableDCache(void); // 禁止DCache

voidMMU_EnableAlignFault(void); // 使能对齐检查

voidMMU_EnableMMU(void); // 使能MMU

voidMMU_DisableMMU(void); // 禁止MMU

voidMMU_SetTTBase(int Base); // Set TTBase

voidMMU_SetDomain(int Domain); // Set Domain

voidMMU_InvalidateICache(void); // 无效ICache

voidMMU_InvalidateDCache(void); // 无效DCache

voidMMU_InvalidateTLB(void); // 无效TLB

voidMMU_SetProcessId(unsigned int pid); // Process ID

voidMMU_Init(void); // MMU页表初始化

unsigned int*MMU_GetTableBase(void); // 获取MMU页表内存地址

voidMMU_SetMTT(unsigned int vaddrStart,unsigned int vaddrEnd,

unsigned int paddrStart,unsignedint attr);

#ifdef__cplusplus

}

#endif

#endif /*__MMU_H__*/

我们在MMU模块MMU.c中实现对段映射的MMU页表的设置初始化,对于寄存器空间,一般是1:1映射且段属性不能开Cache和写缓存,因为寄存器的值可能随时都发生变化,每次读写均应从寄存器处读写。MMU映射除了异常向量表由0x0地址映射到用户异常向量表地址处外,其它空间均1:1映射,对于内存空间,开Cache和写缓存。模块代码实现如下:

#include "MMU.h"

// MMU页表在编译器初始化代码之前调用,分配一个16k对齐16k大小MMU内存段,

// 这里让编译器分配这个全局内存块,一定不能让编译器初始化这部分内存

// 用__attribute__限制为未初始化段,不要让编译器初始化

__align(0x4000) static unsigned char MMU_PageTable[0x4000]

__attribute__((section("MMU_Mem"),zero_init));

unsigned int*MMU_GetTableBase(void)

{

return (unsigned int *)MMU_PageTable;

}

voidMMU_Init(void)

{

// 引入用户代码运行基址,0x0处向量表重映射到用户代码向量表位置处

extern unsigned int __CodeAddr__;

MMU_DisableDCache(); // 禁用DCache

MMU_DisableICache(); // 禁用ICache

MMU_InvalidateDCache(); // 使16K DCache无效

MMU_InvalidateICache(); // 使16K ICache无效

MMU_EnableICache(); // 加快执行MMU_Init

MMU_DisableMMU(); // 禁用MMU

MMU_InvalidateTLB(); // 使无效转换表

//MMU_SetMTT(int vaddrStart,int vaddrEnd,intpaddrStart,int attr)

// 0处异常向量表映射到__CodeAddr__处,代码搬移时己复制用户向量表

// 0地址中断向量表重新映射到代码运行RAM基址,其余默认1:1映射

// 寄存器空间不能开启cache,写缓存,寄存器应为volatile变量

//steppingstone(Nand Boot)

MMU_SetMTT(0x00000000, 0x00000000,__CodeAddr__, RW_CB);

//SROM Bank0 Reserve

MMU_SetMTT(0x00100000, 0x07f00000,0x00100000, RW_NCNB);

//SROM Bank1 Reserve

MMU_SetMTT(0x08000000, 0x0ff00000,0x08000000, RW_NCNB);

//SROM Bank2 Reserve

MMU_SetMTT(0x10000000, 0x17f00000,0x10000000, RW_NCNB);

//SROM Bank3 Reserve

MMU_SetMTT(0x18

查看评论 回复